本文主要是介绍PCIE2—快速实现PCIE接口上下位机通信(二),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

接快速实现PCIE接口上下位机通信(一)

源码链接

4.AXI_MM接口测试

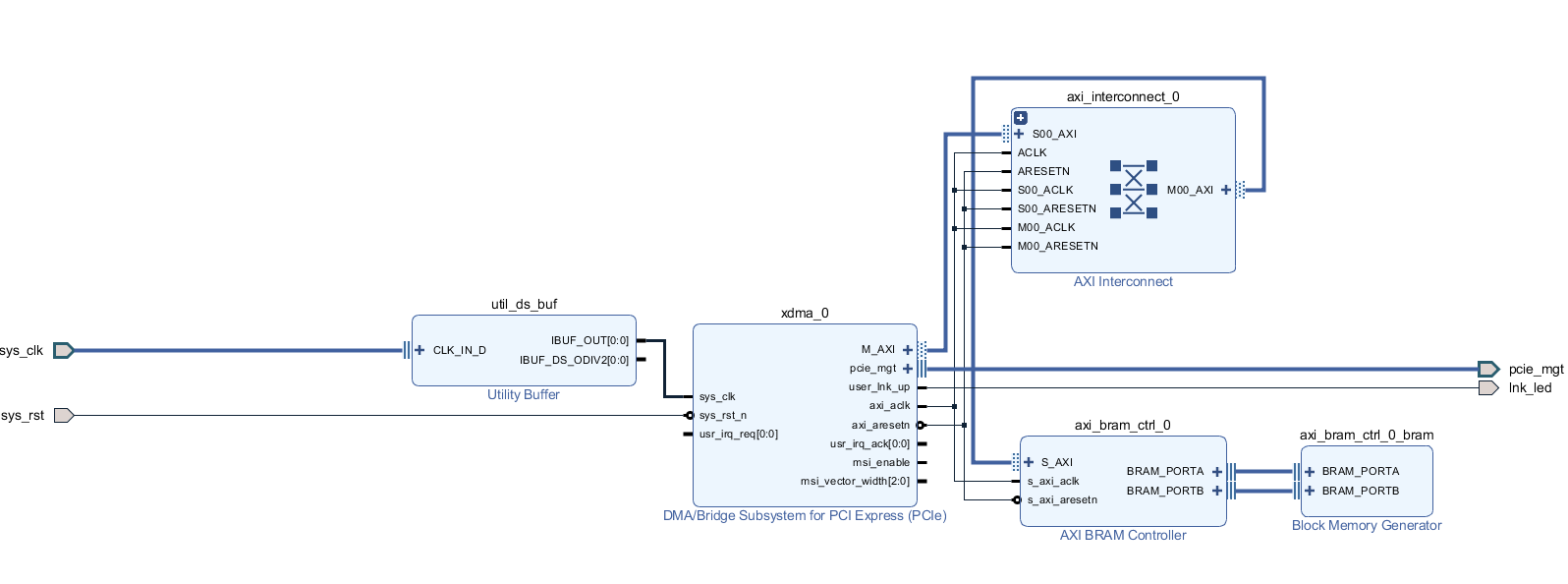

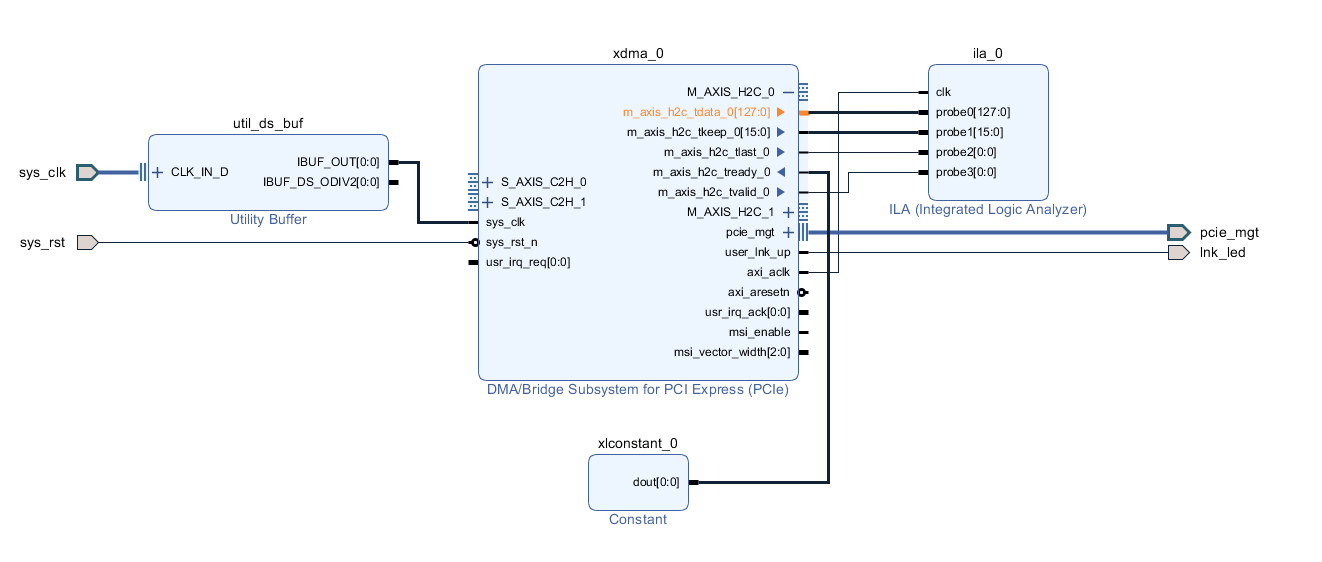

4.1Block design

4.2应用测试

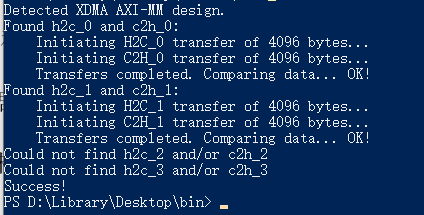

1.xdma_test 应用程序具有以下功能:

✓ 检测 XDMA IP 中启用了多少个 h2c 和 c2h 通道

✓ 检测是否将 XDMA IP 配置为内存映射(AXI-MM)或流(AXI-ST)模式

✓ 在所有可用的 h2c 和 c2h 通道上执行数据传输

✓ 验证写入设备的数据是否与从设备读取的数据匹配

✓ 向用户报告通过或未通过的完成状态

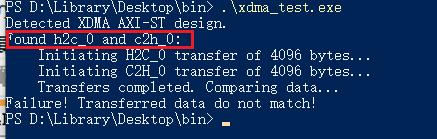

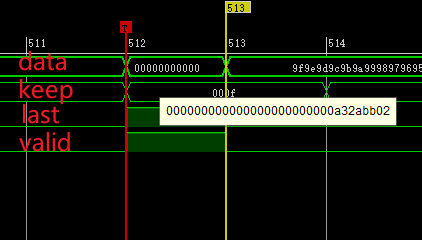

输入.\xdma_test.exe,执行结果如下图所示,检测到的两个DMA通道进行了收发测试均无问题,可以认为XDMA vivado工程无误。

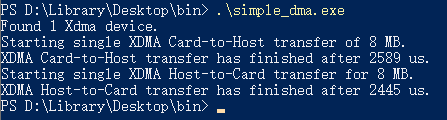

2.simple_dma

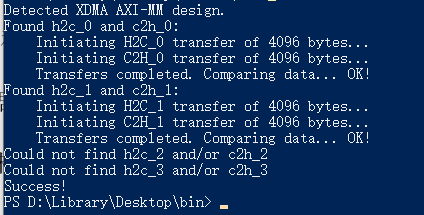

simple_dma 应用程序是简单的测速程序,执行.\simple_dma.exe如下图所示

可计算下行速度8/2445*10^6=3,271MB/s =25.5Gb/s,上行速度8/2589*10^6=3089MB/s=24.1Gb/s,理论速度为5Gb/s*8*0.8=32Gb/s。

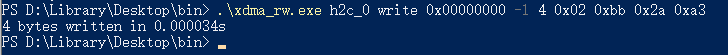

3.xdma_rw.exe

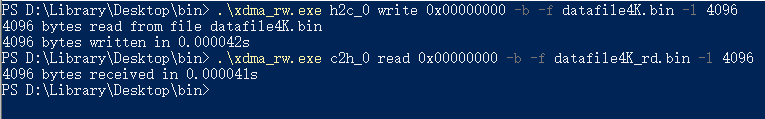

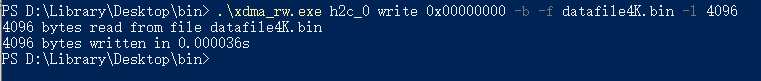

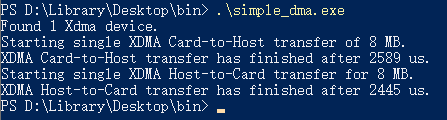

xdma_rw 应用程序可以用来打开任何设备节点并执行读/写操作。通常,这对于读取 control 或 user PCIe BAR 的内存空间很有用。此外,它也可以用于通过 h2c_*和 c2h_*节点执行对齐的 DMA 传输,其中星号表示通道索引(0-1)。默认情况下,该应用程序分配的主机端数据缓冲区是与 PAGE_SIZE 边界(通常为 4kB)对齐的内存。输入.\xdma_rw.exe可以看到输出指示该命令的用法。以下命令代表向h2c_0通道0x00地址写入datafile4K.bin为

.\xdma_rw.exe h2c_0 write 0x00000000 -b -f datafile4K.bin -l 4096

同样从BRAM读回的命令如下:

.\xdma_rw.exe c2h_0 read 0x00000000 -b -f datafile4K_rd.bin -l 4096

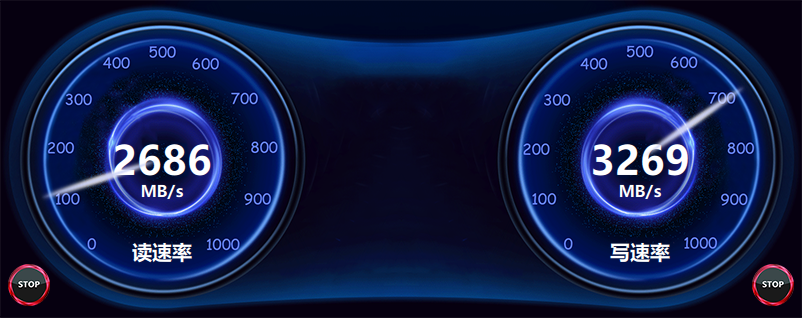

4.3速度测试

使用正电原子测速软件,测试结果如下:

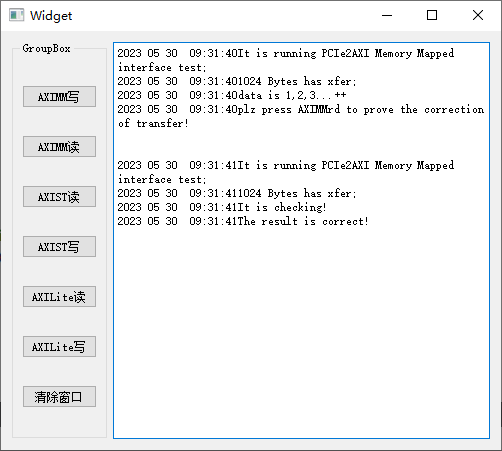

4.4上位机AXIMM测试

5.AXI_ST接口测试

5.1Block Design

5.2应用测试

使用xdma_test.exe能够看到有两个通道。

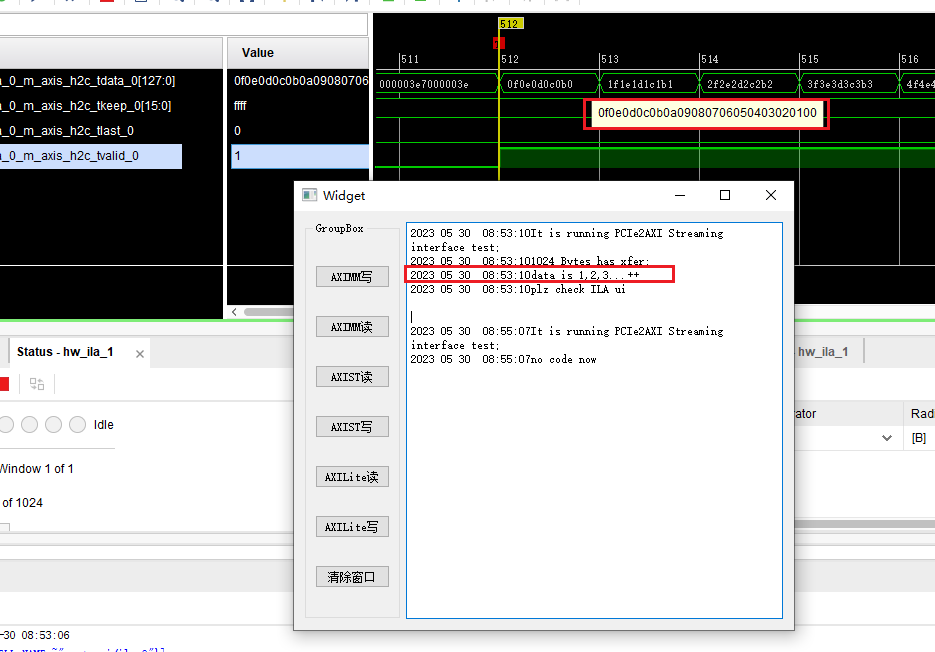

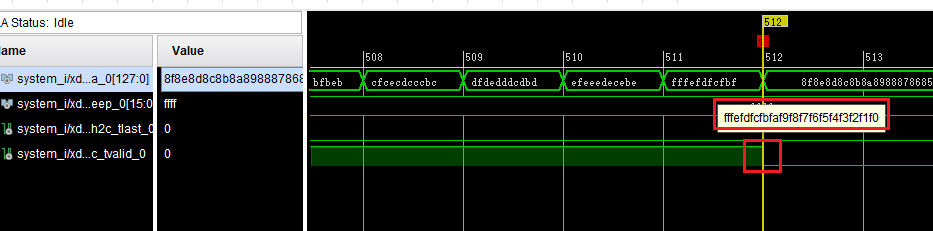

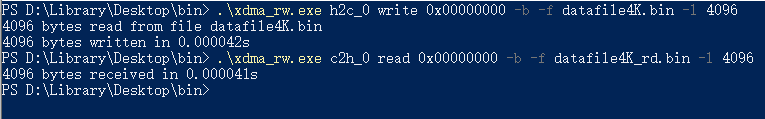

使用xdma_rw.exe向FPGA设备写入4096字节,在下位机抓取数据并做对比。

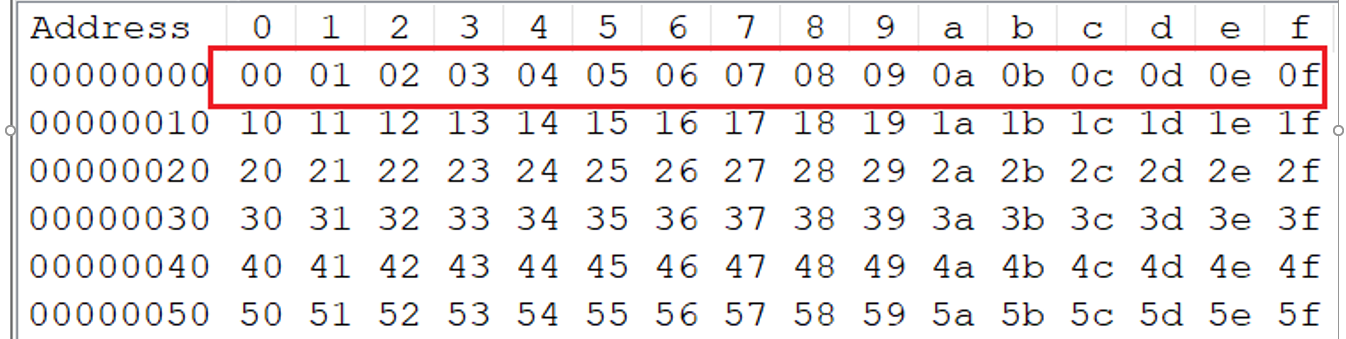

原始数据二进制打开

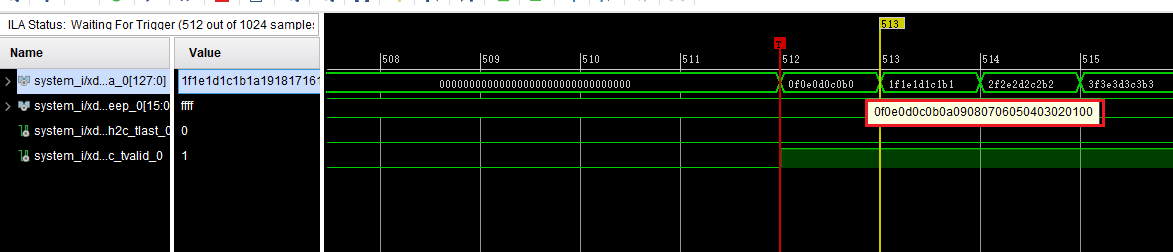

在ILA抓取到的第一个数据

原始数据最后一行

原始数据最后一行

ILA抓取tvalid下降沿

ILA抓取tvalid下降沿

5.3AXI_Streaming时序

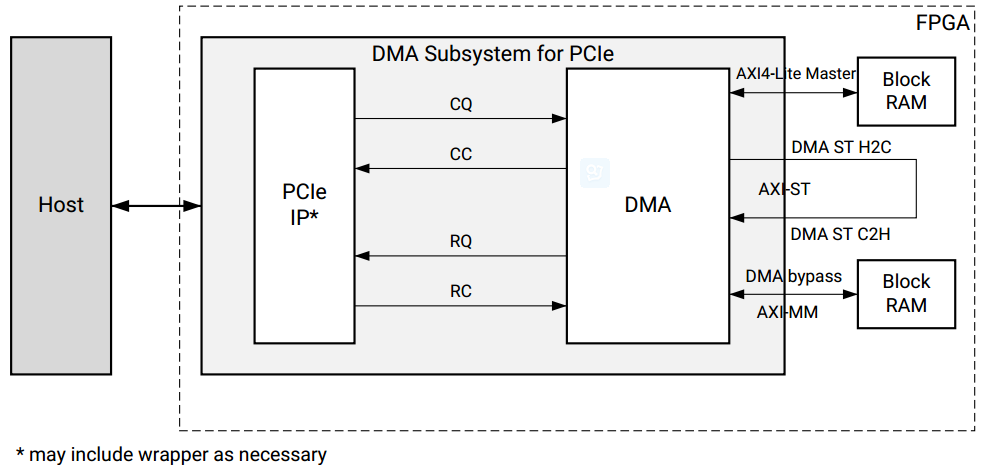

启用PCIe至DMA接口和PCIe至AXILite的AXI4-Stream示例

启用PCIe至DMA接口和PCIe至AXILite的AXI4-Stream示例

AXI4-Stream跟AXI4的区别在于AXI4-Stream没有ADDR接口,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时,允许无限制的数据突发传输规模。AXI4-Stream的核心思想在于流式处理数据。

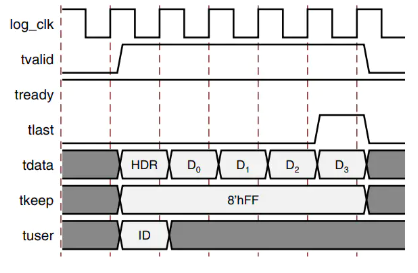

一个AXI-stream传输的时序图:

.

.

AXI-stream传输的时序图

其中AXI-stream一般的数据传输过程如下:

1、首先slave将TREADY信号拉高,表示自己可以接收信号。

2、当master将TDATA,TKEEP,TUSER准备就绪之后,将TVALID拉高,传输开始。

3、其中TKEEP满足TKEEP[x] is associated with TDATA[(8x+7):8x],当其被拉高时表示这段数据必须传输到目的地,请参看下图为实际测试案例,很好的说明了keep的作用。TSTRB表示该段信息是否有效。TUSER可以在传递时捎带用户信息。具体接口参照使用的AXI-stream接口器件,并非所有支持AXI-stream接口的器件都含有以上接口,其中的一些接口是可选的而不是必需的。

4、直到master将TLAST拉高,TVALID拉低,传输结束。

5.4AXIST上位机测试

可以看到,上位机发送的数据是从低字节累加发送的数据,如buf数组,buf[0]=0,buf[1]=1依次累加。在接收端,以128bit为周期,上位机低字节先发送,对应下位机128位宽中的低位。大端模式,是指数据的高字节保存在内存的低地址中,而数据的低字节保存在内存的高地址中。因此PCIE传输是小端模式。(低字节对应低位数据)

6.AXI_Lite接口测试

6.1Block design

6.2应用测试

1.xdma_test 应用程序具有以下功能:

✓ 检测 XDMA IP 中启用了多少个 h2c 和 c2h 通道

✓ 检测是否将 XDMA IP 配置为内存映射(AXI-MM)或流(AXI-ST)模式

✓ 在所有可用的 h2c 和 c2h 通道上执行数据传输

✓ 验证写入设备的数据是否与从设备读取的数据匹配

✓ 向用户报告通过或未通过的完成状态

输入.\xdma_test.exe,执行结果如下图所示,检测到的两个DMA通道进行了收发测试均无问题,可以认为XDMA vivado工程无误。

2.simple_dma

simple_dma 应用程序是简单的测速程序,执行.\simple_dma.exe如下图所示

可计算下行速度8/2445*10^6=3,271MB/s =25.5Gb/s

上行速度8/2589*10^6=3089MB/s=24.1Gb/s

理论速度为5Gb/s*8*0.8=32Gb/s

3.xdma_rw.exe

xdma_rw 应用程序可以用来打开任何设备节点并执行读/写操作。通常,这对于读取 control 或 user PCIe BAR 的内存空间很有用。此外,它也可以用于通过 h2c_*和 c2h_*节点执行对齐的 DMA 传输,其中星号表示通道索引(0-1)。默认情况下,该应用程序分配的主机端数据缓冲区是与 PAGE_SIZE 边界(通常为 4kB)对齐的内存。输入.\xdma_rw.exe可以看到输出指示该命令的用法。以下命令代表向h2c_0通道0x00地址写入datafile4K.bin为

.\xdma_rw.exe h2c_0 write 0x00000000 -b -f datafile4K.bin -l 4096

同样从BRAM读回的命令如下:

.\xdma_rw.exe c2h_0 read 0x00000000 -b -f datafile4K_rd.bin -l 4096

测试结果如下:

6.3上位机测试

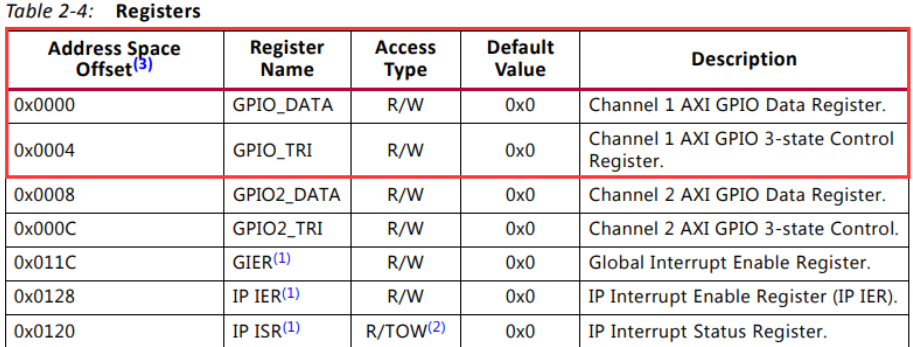

本例程使能了user通道,即xdma的AXI-Lite通道,允许上位机读写FPGA侧用户侧逻辑,通过AXI-GPIO ip来验证该功能。使能GPIO ip核的输入和输出通道,将输入位宽配置成2并连接两个按键,即验证FPGA侧用户侧输入上位机接收;将输出位宽配置成2并连接两个LED灯,即验证上位机输入,FPGA侧用户侧响应。需要注意的是,上位机读写是通过XDMA的AXI Lite接口访问GPIO ip的寄存器完成的,因此应该明确在位于多少偏移地址的寄存器能够读取到当前IO的写入值,应该明确在位于多少偏移地址的寄存器能够配置当前IO的输出值,如下图所示,即为该GPIO IP核的寄存器说明。

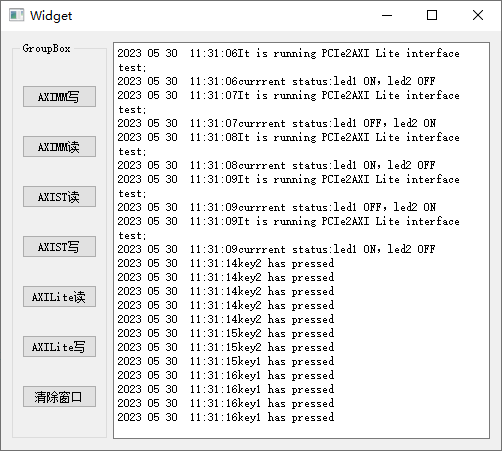

下图所示为上位机与该例程通信的结果,当点击“AXILite写”时,将切换当前两个LED的亮灭状态,并在界面显示当前状态,实测与开发板LED状态一致;当点击“AXILite读”时,程序将启动定时器每100ms读取一次FPGA侧用户侧即GPIO的输入管脚的状态,因此当在开发板按下key按键的时候,上位机会“实时”检测结果。

7.PCIE调试问题

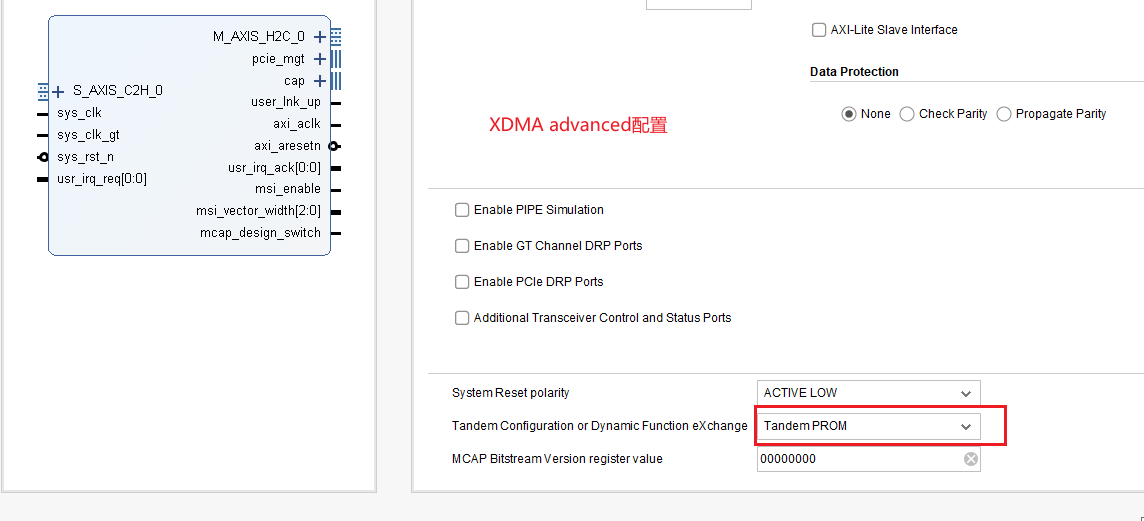

①Flash启动时间长,导致主机无法检测到PCIE设备,在添加Tandem配置后,解决此问题。

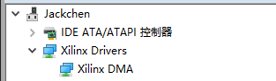

②7系列的PCIE2.0在vivado2020版本上无法识别,KU系列的PCIE3.0在vivado2020.2版本上测试,可以识别。

③测试下发速度为: 5986MB/s=5986/1024=5.84GB/s=46.76Gbps (理论是8Gbps*8=64Gbps),如图所示。

这篇关于PCIE2—快速实现PCIE接口上下位机通信(二)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!