本文主要是介绍ZYNQ 调用AXI WR RD ip及其代码,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

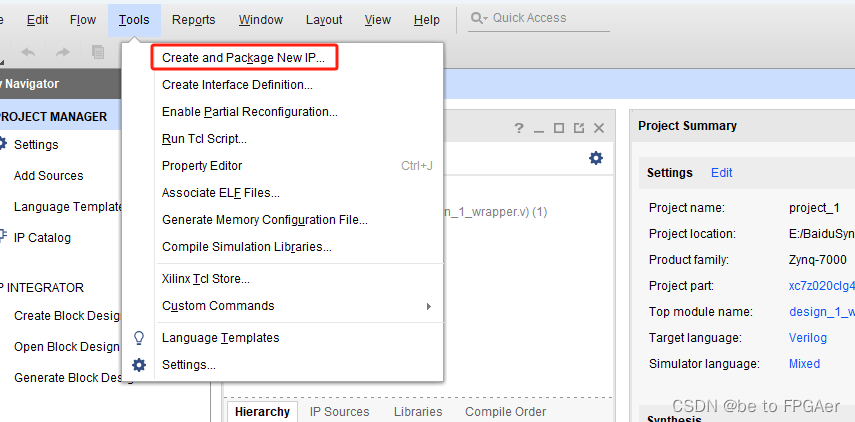

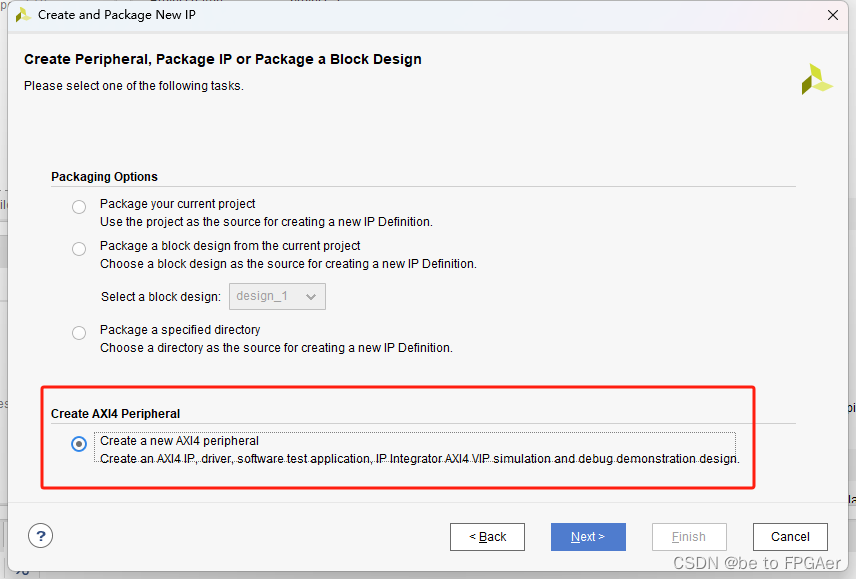

首先调用ip

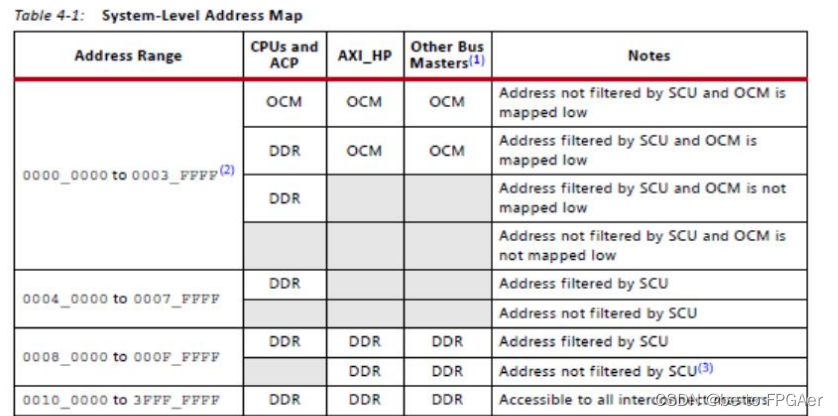

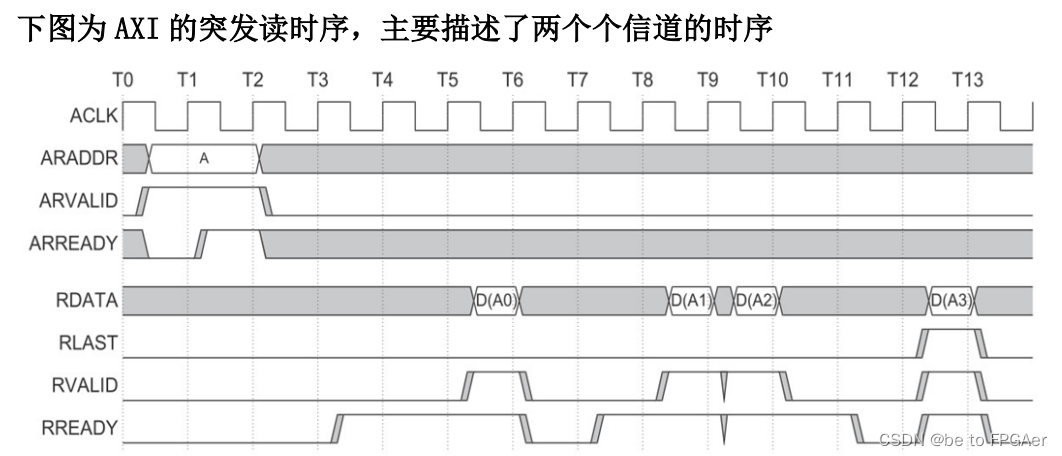

值得注意的是:zynq支持axi4.0 ,但是创建的ip是属于axi3.0,其区别主要是在数据位宽以及突发长度的区别。

下面附读写控制模块(稍作修改就可使用,数据位宽是64bit 突发长度是256):

assign fifo_wr_data = {8'd0,pixel_rgb};assign fifo_wr_en = hv;//fifo 2 clock domain switchasfifo_wr32x4096_rd64x2048 asfifo_wr32x4096_rd64x2048inst (.wr_clk(pixel_clk), // input wire wr_clk.rd_clk(M_AXI_ACLK), // input wire rd_clk.din(fifo_wr_data), // input wire [31 : 0] din.wr_en(fifo_wr_en), // input wire wr_en.rd_en(fifo_rd_en), // input wire rd_en.dout(fifo_rd_data), // output wire [63 : 0] dout.full(), // output wire full.empty(), // output wire empty.rd_data_count(rd_data_count) // output wire [10 : 0] rd_data_count

);//dma write channel assign fifo_rd_en = axi_wvalid & M_AXI_WREADY;always @(posedge M_AXI_ACLK) beginif(M_AXI_ARESETN == 1'b0) beginburst_start <= 1'b0;endelse if (rd_data_count >='d256 && axi_wvalid == 1'b0 && axi_awvalid == 1'b0) beginburst_start <= 1'b1;endelse beginburst_start <= 1'b0;endendalways @(posedge M_AXI_ACLK) beginif(M_AXI_ARESETN == 1'b0) beginaxi_awvalid <= 1'b0;endelse if (axi_awvalid == 1'b1 &&M_AXI_AWREADY == 1'b1) beginaxi_awvalid <= 1'b0;endelse if (burst_start == 1'b1 && axi_awvalid == 1'b0 && axi_wvalid == 1'b0) beginaxi_awvalid <= 1'b1;endendalways @(posedge M_AXI_ACLK) beginif(M_AXI_ARESETN == 1'b0) beginaxi_awaddr <= 'd0;endelse if (M_AXI_AWREADY == 1'b1 && axi_awvalid == 1'b1 && axi_awaddr == 'd8292352) beginaxi_awaddr <= 'd0;endelse if (M_AXI_AWREADY == 1'b1 && axi_awvalid == 1'b1) beginaxi_awaddr <= axi_awaddr + 'd2048;endendalways @(posedge M_AXI_ACLK) beginif(M_AXI_ARESETN == 1'b0) beginaxi_wvalid <= 1'b0;endelse if (M_AXI_WREADY == 1'b1 && axi_wvalid == 1'b1 && burst_cnt == 'd255) begin //burst endaxi_wvalid <= 1'b0;endelse if (M_AXI_AWREADY == 1'b1 && axi_awvalid == 1'b1) beginaxi_wvalid <= 1'b1;endendalways @(posedge M_AXI_ACLK) beginif(M_AXI_ARESETN == 1'b0) beginburst_cnt <='d0;endelse if (M_AXI_WREADY == 1'b1 && axi_wvalid == 1'b1 && burst_cnt == 'd255) beginburst_cnt <= 'd0;endelse if (M_AXI_WREADY == 1'b1 && axi_wvalid == 1'b1) beginburst_cnt <= burst_cnt + 1'b1;endendalways @* beginif(M_AXI_WREADY == 1'b1 && axi_wvalid == 1'b1 && burst_cnt == 'd255) beginaxi_wlast <= 1'b1;endelse beginaxi_wlast <= 1'b0;endendalways @* beginaxi_wdata = fifo_rd_data;endalways @(posedge M_AXI_ACLK) beginif(M_AXI_ARESETN == 1'b0) beginaxi_bready <= 1'b0;endelse beginaxi_bready <= 1'b1;endend写模块代码(数据位宽是64bit 突发长度是256):

reg [7:0]rx_Cnt;always @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0 ) begin axi_arvalid<=1'b0; endelse if(axi_arvalid==1'b1 && M_AXI_ARREADY==1'b1)beginaxi_arvalid<=1'b0; end else if(rd_data_count<=1024 && axi_arvalid==1'b0 && axi_rready==1'b0 ) begin axi_arvalid<=1'b1; end endalways @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0 ) begin axi_araddr<='d0; endelse if(axi_arvalid==1'b1 && M_AXI_ARREADY==1'b1 && axi_araddr=='d8292352)beginaxi_araddr<='d0; end else if(axi_arvalid==1'b1 && M_AXI_ARREADY==1'b1) begin axi_araddr<=axi_araddr+'d2048; end endalways @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0 ) begin axi_rready<=1'b0; endelse if(M_AXI_RVALID==1'b1 && M_AXI_RREADY==1'b1 && rx_Cnt=='d255)beginaxi_rready<=1'b0; end else if(axi_arvalid==1'b1 && M_AXI_ARREADY==1'b1) begin axi_rready<=1'b1; end endalways @(posedge M_AXI_ACLK) begin if (M_AXI_ARESETN == 0 ) begin rx_Cnt <= 'd0; endelse if(M_AXI_RVALID==1'b1 && M_AXI_RREADY==1'b1 && rx_Cnt=='d255)beginrx_Cnt <='d0; end else if(M_AXI_RVALID==1'b1 && M_AXI_RREADY==1'b1) begin rx_Cnt<=rx_Cnt+1'b1; end end// Add user logic herefifo_generator_0 fifo_generator_0inst (.wr_clk(M_AXI_ACLK), // input wire wr_clk.rd_clk(hdmi_clk), // input wire rd_clk.din(M_AXI_RDATA), // input wire [63 : 0] din.wr_en(M_AXI_RVALID==1'b1 && M_AXI_RREADY==1'b1), // input wire wr_en.rd_en(rd_fifo_en), // input wire rd_en.dout(pixel_rgb), // output wire [31 : 0] dout.full(), // output wire full.empty(), // output wire empty.rd_data_count(rd_data_count) // output wire [10 : 0] rd_data_count

);这篇关于ZYNQ 调用AXI WR RD ip及其代码的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!