本文主要是介绍SDC文件常用时序约束语句,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

SDC可以帮助工具进行静态时序分析。在SDC中首先需要创建时钟以及时钟间对应的关系,需要注意的是,时钟间的关系(同步还是异步),并不是由时钟间本身的关系决定的,而是由SDC文件的约束决定的。即使是两个同频同相的时钟,SDC也可以将其设为异步时钟,这样工具就不会将这两个时钟作为同步时钟来进行STA分析,布线时无需考虑这两个时钟下的信号交互时所需的建立时间和保持时间;在这种情况下,这两个时钟下的信号进行交互时需要进行CDC处理,否则像spyglass一类的工具会报告CDC违例。

正是因为时钟间的关系是需要用户指定的,因此SDC需要描述generated_clock的特性。虽然理论上虽然工具可以根据master clock来分析出generated_clock的频率和相位关系,但无法分辨用户需要将这些时钟看作是同步还是异步的。如果用户不定义generated_clock,那么一个master clock衍生的所有时钟都会被看作同步的,这可能不符合用户的实际需要。另外,工具并不是万能的,某些情况下工具可能无法分析出generated_clock的准确频率与相位关系,因此generated_clock的定义是很有必要的。

时钟约束

1. 基本约束

create_clocks -name clk_name -period 10 [get_ports clk_in]

这是最基本的时钟约束语句,为时钟管脚创建一个时钟,综合工具会根据创建的时钟进行布局布线,并给出时序分析报告,若发生时序违例,则需要对设计进行优化修改。

2.时序约束例外

(1)假路径约束

例:set_false_path -from [get_clocks clka] -to [get_clocks clkb]

set_false_path 是指定不希望EDA工具进行分析的路径,可以是与电路正常工作不相关的测试逻辑或静态逻辑,也可以是跨时钟域的异步路径。但是set_false_path 只能指定单方向路径的timing exceptions。如果需要指定双向的timing exceptions,则需要:

set_false_path -from [get_clocks clka] -to [get_clocks clkb]

set_false_path -from [get_clocks clkb] -to [get_clocks clka]

使用set_clock_groups -asynchronous -group clka -group clkb 则更为简洁。同时set_clock_groups可以对一个时钟组的多个时钟进行约束,详细内容见链接:set_false_path和set_clock_groups有什么区别? - 知乎

(2)多周期约束

例:set_multiple_path

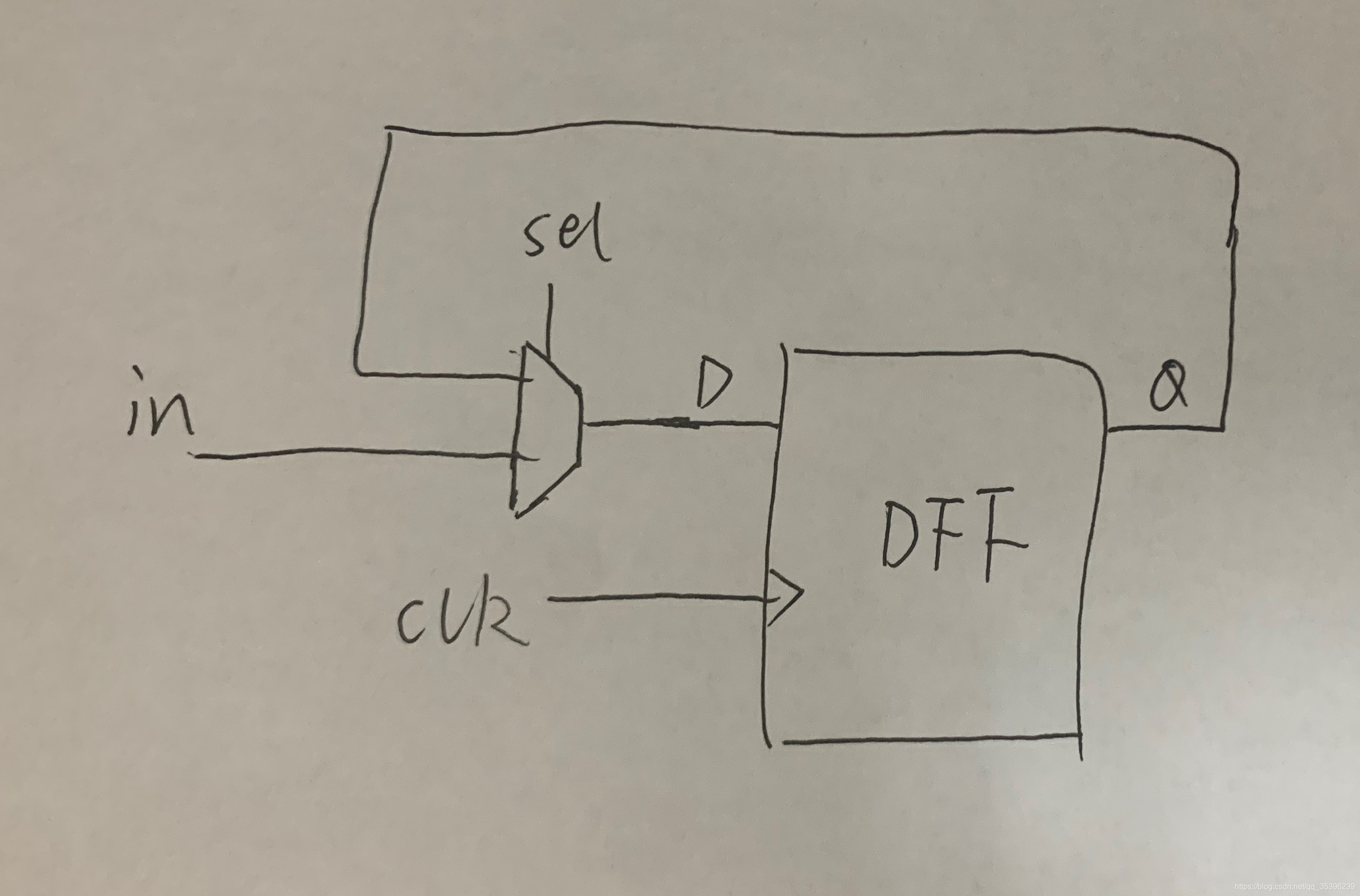

多周期约束是指两个寄存器之间需要多个时钟才能稳定的路径,一般用于组合逻辑较大的路径。使用下图的方法数据稳定,避免出现亚稳态。

二、同步 IO约束

1. 系统同步约束

系统同步是指源端和目的端的时钟由系统提供,不由某一方提供,即PCB板上的时钟接入到FPGA作为FPGA的时钟使用,同时也接入到与FPGA通信的外部芯片中作为外部芯片的时钟使用。

(1)set_input_delay

XILINK文档对set_input_delay的描述是:The set_input_delay command specifies the input path delay on an input port relative to a clock edge at the interface of the design.

说白了就是指定输入数据和时钟的相位差,以便EDA工具分析是否内部寄存器的建立保持时间是否得到满足。这个相位差可以为正也可以为负,主要取决于数据与时钟到达的先后顺序。数据比时钟后到达,则 input_delay 为正,否则 input_delay 为负。

(2)set_output_delay

XILINK文档对set_output_delay的描述是:The set_output_delay command specifies the output path delay of an output port relative to a clock edge at the interface of the design.

与set_input_delay 类似,set_output_delay是指输出数据到达FPGA外部寄存器 和 时钟到达外部寄存器的相位差,很显然,FPGA内部是无法分析外部寄存器的建立时间是多少的,因此,外部寄存器的建立时间要求 是隐含在 set_output_delay 之中的,即set_output_delay即包含了数据的外部走线延迟,也包含了外部寄存器的建立时间要求。VIVADO进行分析时,只是比较 (数据在FPGA内部延迟 + set_output_delay)是否 大于 一个时钟周期,而不去考虑外部寄存器的建立时间,因为外部寄存器的建立时间已经隐含在set_output_delay之中了。对于EDA工具而言,就是尽量减小数据在FPGA内部的延迟,让时序需求得到满足。对于保持时间的分析也同建立时间类似。

2. 源同步约束

源同步是指数据和时钟都由发送端传送而来,其分析与系统同步的分析类似,set_input_delay也是代表数据与时钟的相位差,但由于数据和时钟都由发送发提供,那么一般情况下数据和时钟的相位差就会非常小,因为都需要经历FPGA内部延迟和外部的走线延迟,那么两者的相位差就会比较小。另外与系统同步约束不同的是,假如FPGA为数据发送方,并提供时钟,那么很显然时钟相位是可控的,在控制输出时钟的相位的基础上,则需要对输出时钟作进一步的约束。例如FPGA设计DDR SDRAM的控制器时,就可以使用PLL生成一个随路时钟,改变时钟的相位后,作为DDR SDRAM的时钟进行输出,以此来满足DDR SDRAM的时序要求。

三、异步IO约束

指定输入管脚 到 输出管脚 之间的组合逻辑 的 最大延时和最小延时

set_max_delay 10.0 -from [get_ports in_port] -to [get_ports out_port]

set_min_delay 5.0 -from [get_ports in_port] -to [get_ports out_port]

关于虚拟时钟:

对于输入的端口而言,一般而言是需要设置input delay的。但若该信号只有数据信号,没有随路时钟,我们该如何设置input delay呢?此时就需要创建虚拟时钟,来作为此信号的时钟进行时序分析,如下:

create_clock -name VIR_CLK -period 10

set_input_delay -max 5 -clock VIR_CLK [get_ports data_in]

set_input_delay -min 2 -clock VIR_CLK [get_ports data_in]

当然,如果data_in这个信号在片内被CLKA的DFF使用了,此时可以将data_in的input delay时钟设为CLKA,但此时就认为产生data_in的片外时钟与CLKA是同一个时钟,实际情况一般并不是这样。当然,如果产生data_in的时钟确实与CLKA是同步的,我们可以通过调整set_input_delay的值来抵消skew的影响,但将这些信息杂糅在一起并不是符合设计规范。同时若产生data_in的时钟与CLKA是异步时钟,此时就更需要创建虚拟时钟作为data_in的时钟,并将虚拟时钟与CLKA作为异步时钟来进行处理。

一般而言,虚拟时钟并不是说不存在这个时钟,而是说这个时钟不在片上,需要创建虚拟时钟来告诉EDA工具没有随路时钟的数据端口输入其外部时钟是什么样的。

这篇关于SDC文件常用时序约束语句的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!