本文主要是介绍SAR ADC系列7:采样开关种类(2023.7.31更新版),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

单MOS管开关

传输门开关

如何选取MOS管尺寸

栅压自举开关(Bootstrap)

栅压自举开关实现:

栅压自举开关实现(PMOS衬底连接):

栅压自举开关非理想特性:

衬偏效应消除(要工艺支持)

(以下是更新)

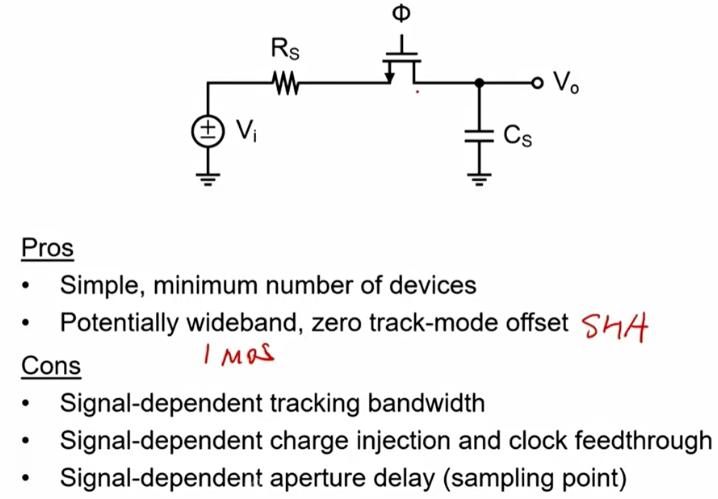

简单的单管开关

优点:①简单、用最少的器件

②带宽大,track-mode offset 小

缺点:①信号相关的TBW——单管开关的显著缺点

②信号相关的电荷注入和时钟馈通——共性,单管开关更加明显

③信号相关的aperture delay(sampling point)——取决于clk-SR、Vin-BW

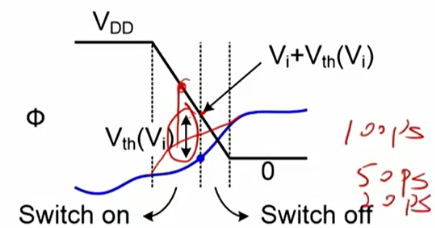

下面对Signal-dependent Aperture Delay进行简单说明

由于clk下降沿不够陡峭,开关在电压小于Vin+Vth时才会关断。Vin的幅度不同导致开关关断时间不同。比如:可能幅值较低是在100ps时关断,幅值较高时在50ps时关断。类似于clock jitter。

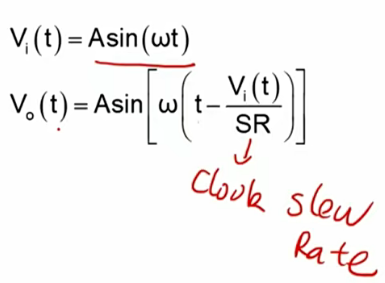

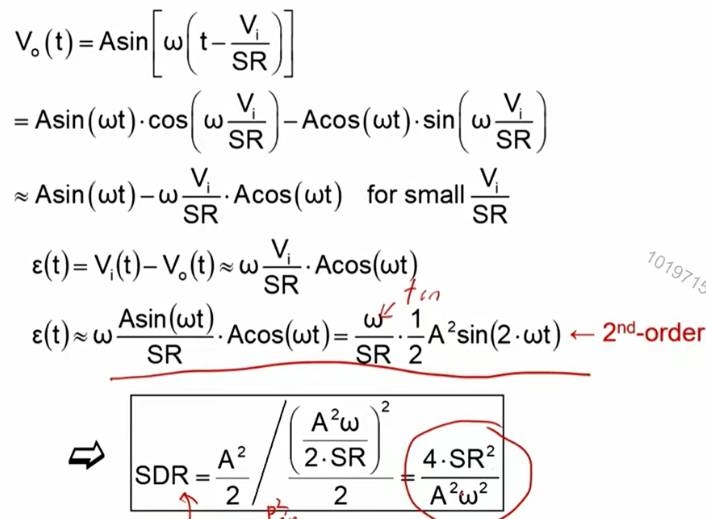

Distortion的定量分析如下:

clk-SR越大,SDR越好。反而信号幅值A越大,信号频率fin越大,SDR越差。

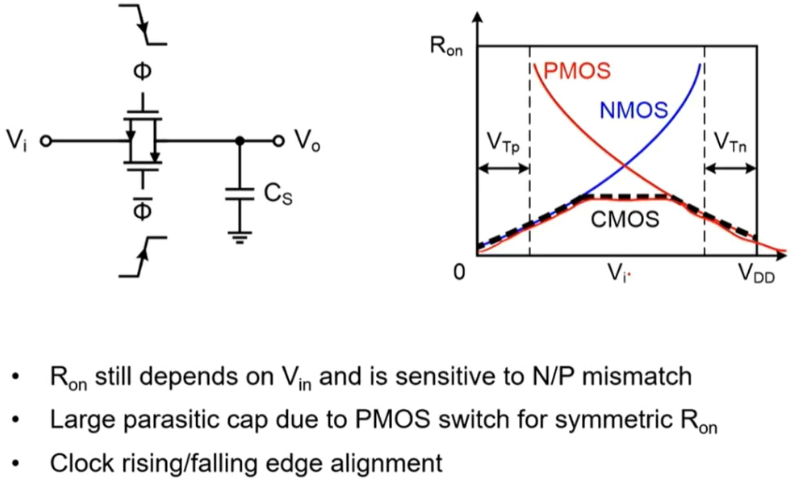

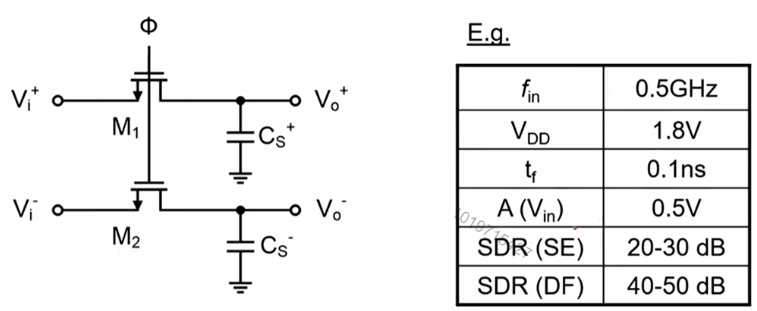

CMOS开关(传输门结构)

■ 改善了Signal-dependent-Ron,但是还是存在Ron的非线性。并且对N/P的失配较为敏感。

■ Pmos为了获得Nmos对称的Ron,需要尺寸较大,导致较大的寄生电容。

■ 一定程度改善了clock-feedthrough。对时钟上升/下降沿的对齐有要求。

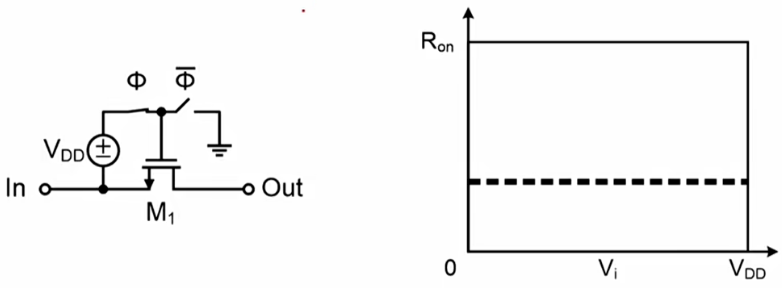

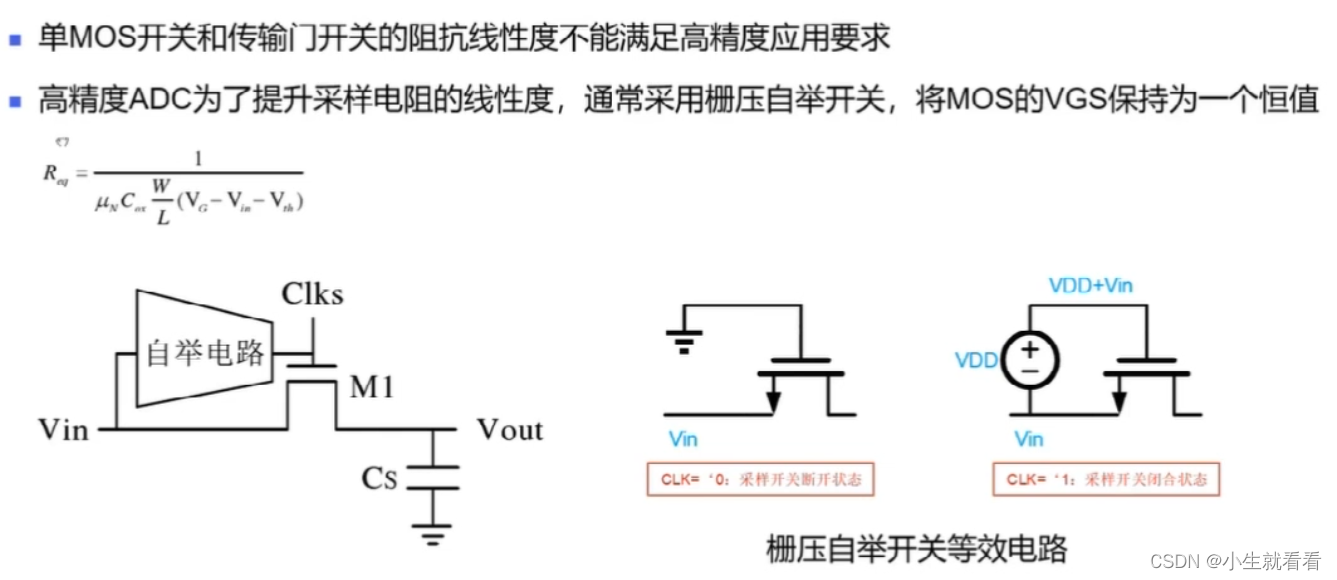

Boostrap开关(自举开关)

导通时具有恒定的栅极驱动电压,Vgs = Vdd,关断时,Vgs = 0。这样在一阶情况下,Ron不依赖Vin,消除了非线性,同时Nmos具有更小的寄生电容。(考虑二阶的体效应,Ron和Vin还是有关系的)。

开关关断瞬间,栅极电压是从 Vdd+Vin -->gnd 。clock-feedthrough or charge sharing 影响更大,并且和Vin相关,导致非线性。

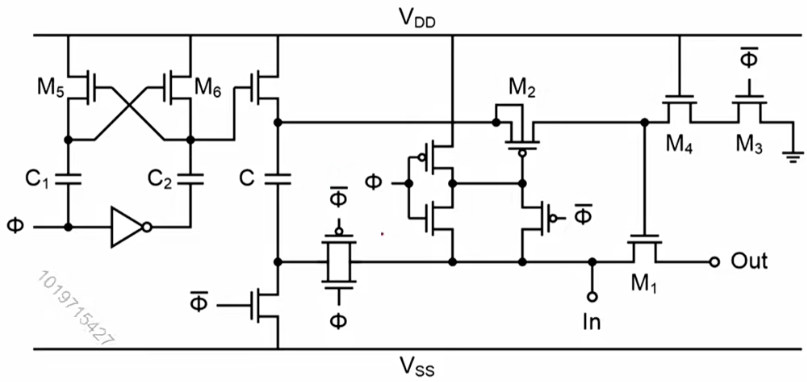

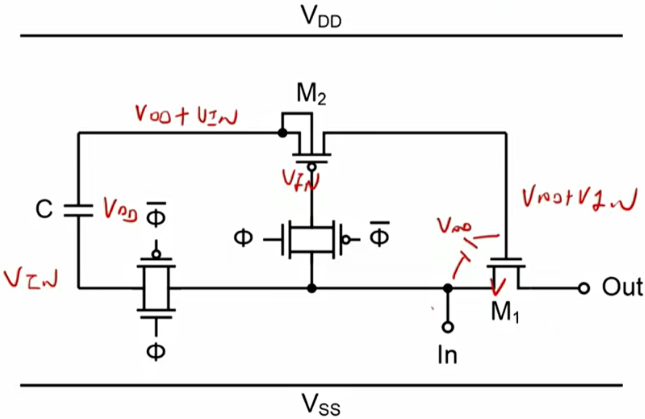

早期的Boostrap开关如下:

工作过程如下:

φ=0 时,将C充电至Vdd。同时M2断开,M3导通,将开关M1的栅拉倒gnd,hold,开关断开。

φ=1 时,将Vin传输到C的下级板,C上级板抬升到Vdd+Vin,同时M2的栅压也为Vin,M2的 Vgs= -Vdd,M2将电容上级板电压Vdd+Vin传到开关M1的栅极,这样M1的Vgs = Vdd,track,导通。

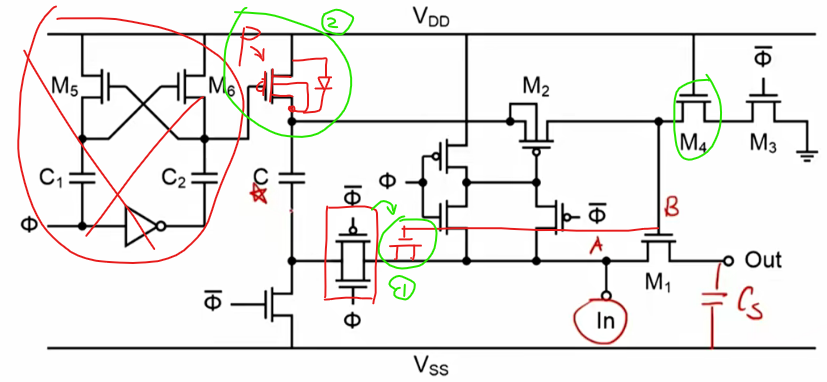

改进:

①传输门的作用是将Vin传输到C的下级板,传输门的优点是Ron较为恒定,没有阈值电压损失,并且是时钟驱动。改成单个Nmos更加简单,将Nmos的栅极也接到Bootstrap点,同样可以无损传输。缺点是C的上级板要多驱动一个这个Nmos管。

②将Nmos换成Pmos,省掉一大坨驱动电路。同样可以将Vdd传到C的上级板,需要注意的是Pmos的Body接法,接到C的上级板,否则Pmos的寄生二极管会将Boostrap电压钳位住,min{Vdd+Vin, Vdd+V_dio}。

③常通的Nmos_M4的作用是分压,保护M3。当φ=0 时,如果没有M4,M3的一端接gnd,另一端接Vdd+Vin,有耐压问题,有损寿命,可靠性。并且M4常开的Nmos,不影响M3正常工作。

④(看简化后的电路图)M5由Pmos换成了Nmos,M5和M3是互补的。M3受clk控制的,其Vgs=Vdd-Vin,当Vin过大可能会关断。但是,M3一导通就将M6电压下拉到gnd使得M6导通,Boostrap电压立马传到G点,G点拉高使得M5导通,M5的Vgs=Vin,这样即使M3关断也没关系。缺点就是G点又多驱动一个Mos管。

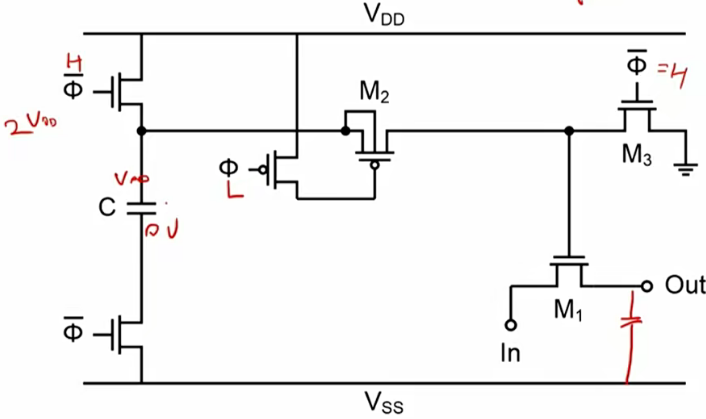

简化后的电路:

Cb和C2、Cg进行电荷共享,存在分压,使得G点电压达不到理想的Vdd+Vin。

存在的问题:

①G点寄生电容高阶模型也是随Vin在变换,非线性。

②G点的电压是从 [Vdd+Vin -- 0 ]在变化,clk-feedthrough charge sharing 非常明显,非线性。为什么不说 channel charge injection呢?因为Vgs = Vdd,一阶上来看是个和输入不相关的量,相当于DC offset。做全差分 或 dummy 可以改善。

③Nmos开关管的body leakage。

④Ron非线性一阶消除,但是考虑高阶效应,Ron还是与输入信号相关,导致非线性。(衬偏效应,Vth和Vsb有关,即Vth和Vin有关,导致Ron和Vin相关)

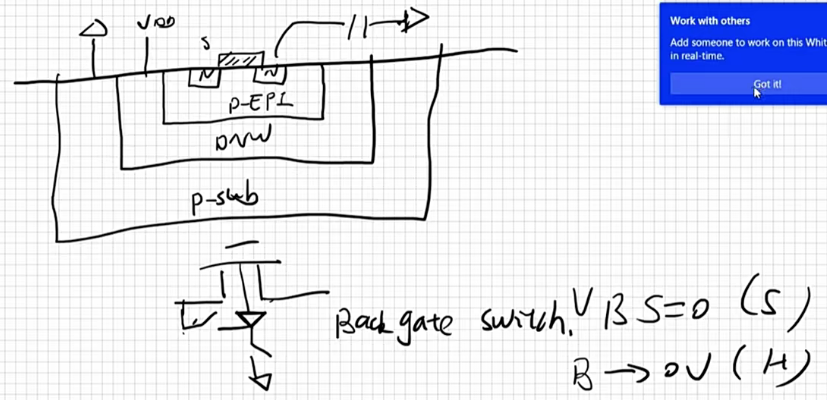

解决衬偏效应(背栅效应 back gate effect):用深n阱工艺做开关管。

此时要注意:做 back gate switch。即 Track阶段——Body = Source,可以消除衬偏效应带来的非线性,恒定阻抗;Hold阶段——Body = gnd,防止寄生二极管导通。

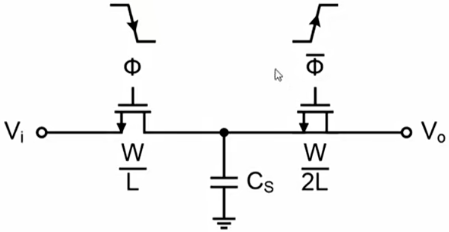

Dummy Switch

Dummy器件和开关管时钟反向,尺寸大约为开关管尺寸的一半。假设开关断开瞬间,Channel Charge 均匀向两边注入,也就是Cs这一端被注入 Qch/2 ,而 dummy switch尺寸刚好为(W/L)/2,开关打开,表面需要电荷形成反型层沟道,把开关管的charge injection补偿掉。并且也能对时钟馈通 clock-feedthrough 进行补偿。

当然大部分情况下Chage Injection并不是两边均分的,但是补偿总比不补偿好,在加上全差分,能够消除大部分distortion了。

Full-Differential T/H

消除偶次谐波失真,包括信号相关的aperture delay 也被减小。

(以下是旧版)

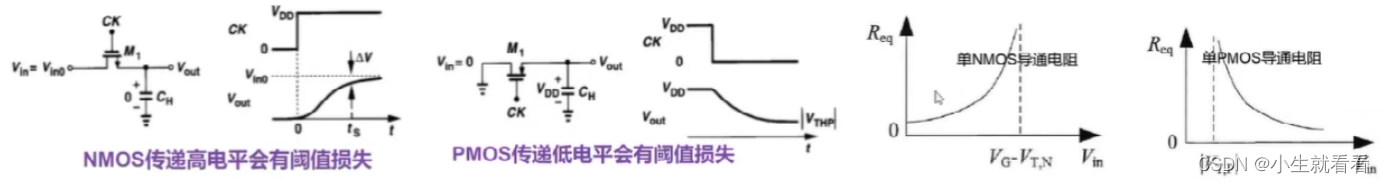

单MOS管开关

单MOS可以作为采样开关使用,工作在线性区。Id=uCoxW/L*(Vg-Vin-Vth)*Vds,得出:

![]()

由于 Req 和 Vin 有关,所以开关线性度很差,并且存在阈值电压损失问题。

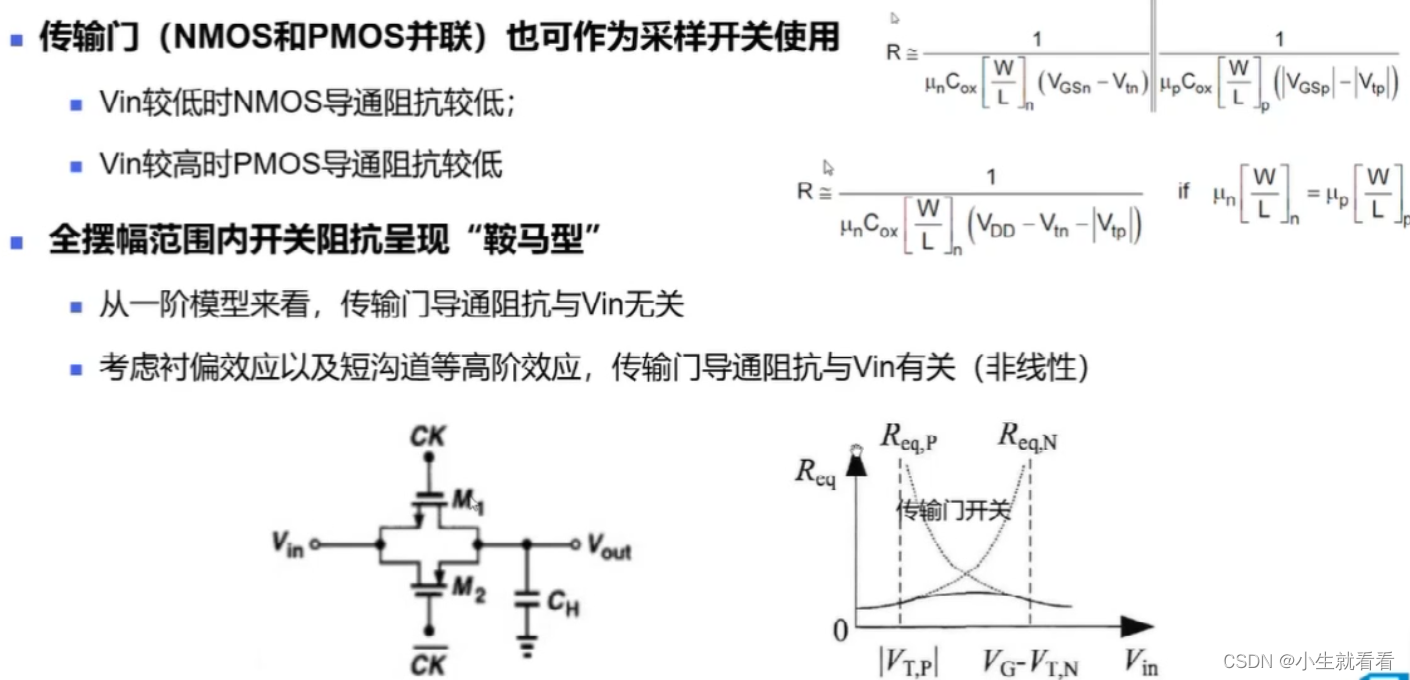

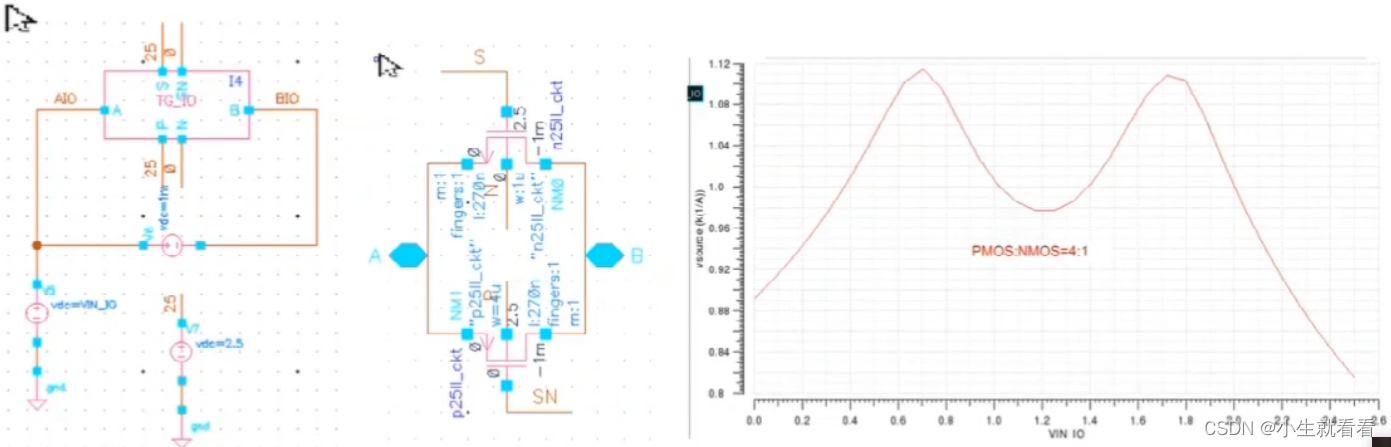

传输门开关

衬偏效应和短沟道效应等高阶效应,使得Vth随Vin变化,进而Req还是随着Vin变化,线性度不太好

如何选取MOS管尺寸

由于电子空穴迁移率差异,PMOS和NMOS尺寸比约为 4:1 才能保存对称马鞍形。

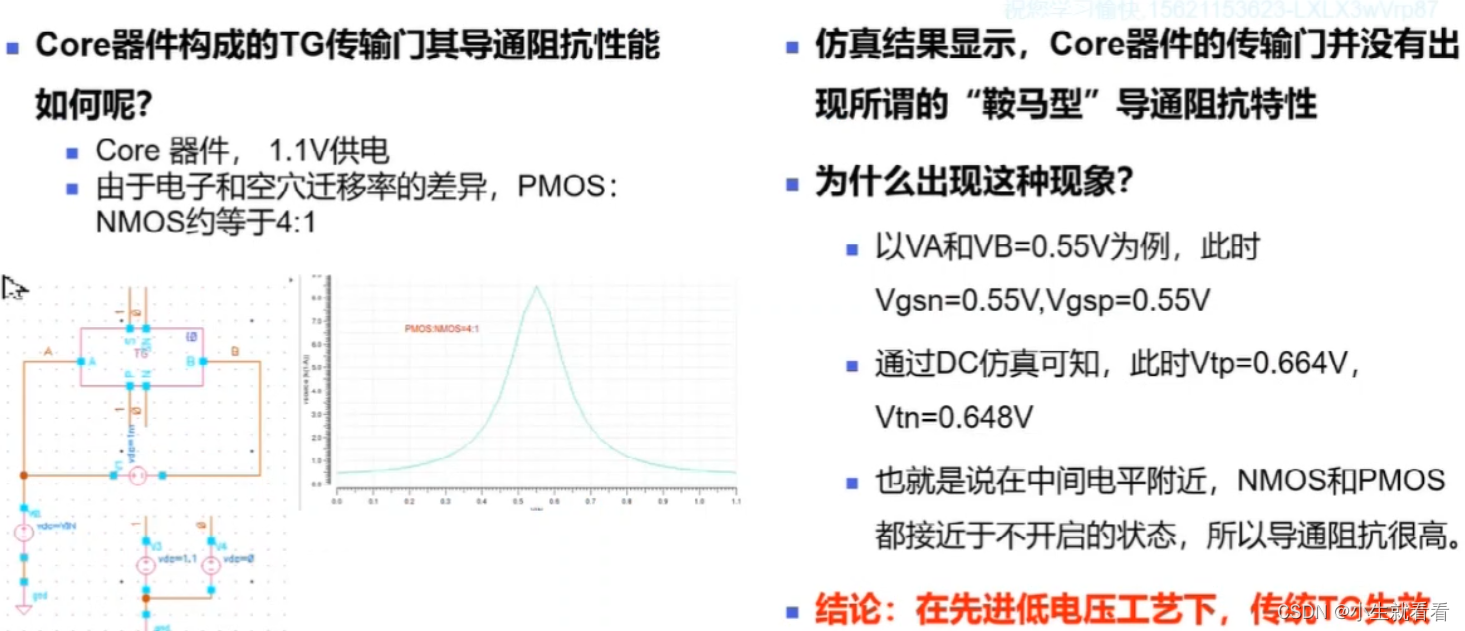

栅压自举开关(Bootstrap)

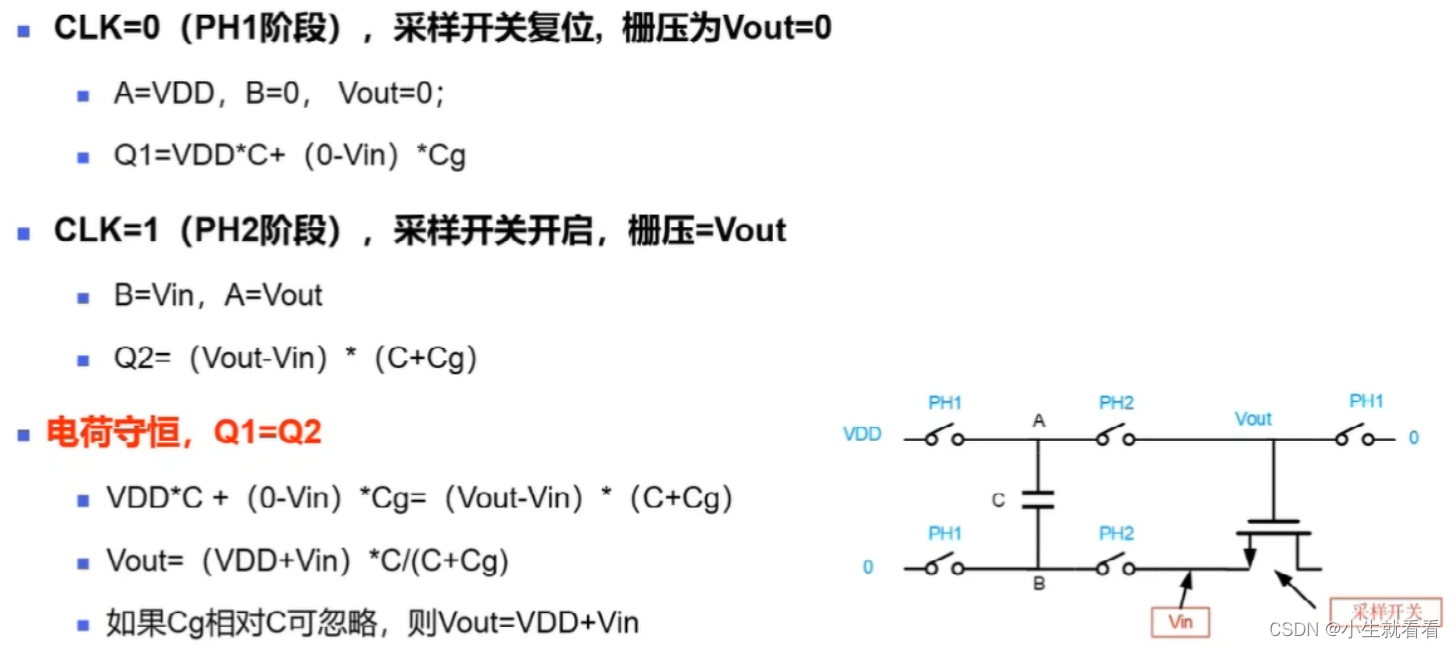

■ 简单的 Pump,CLK=0 电容充电到VDD,CLK=1 电容下级板抬到Vin,电荷守恒上级板抬到 Vin+VDD。

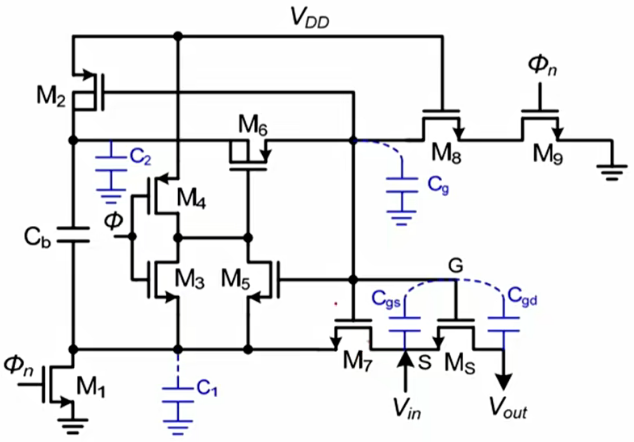

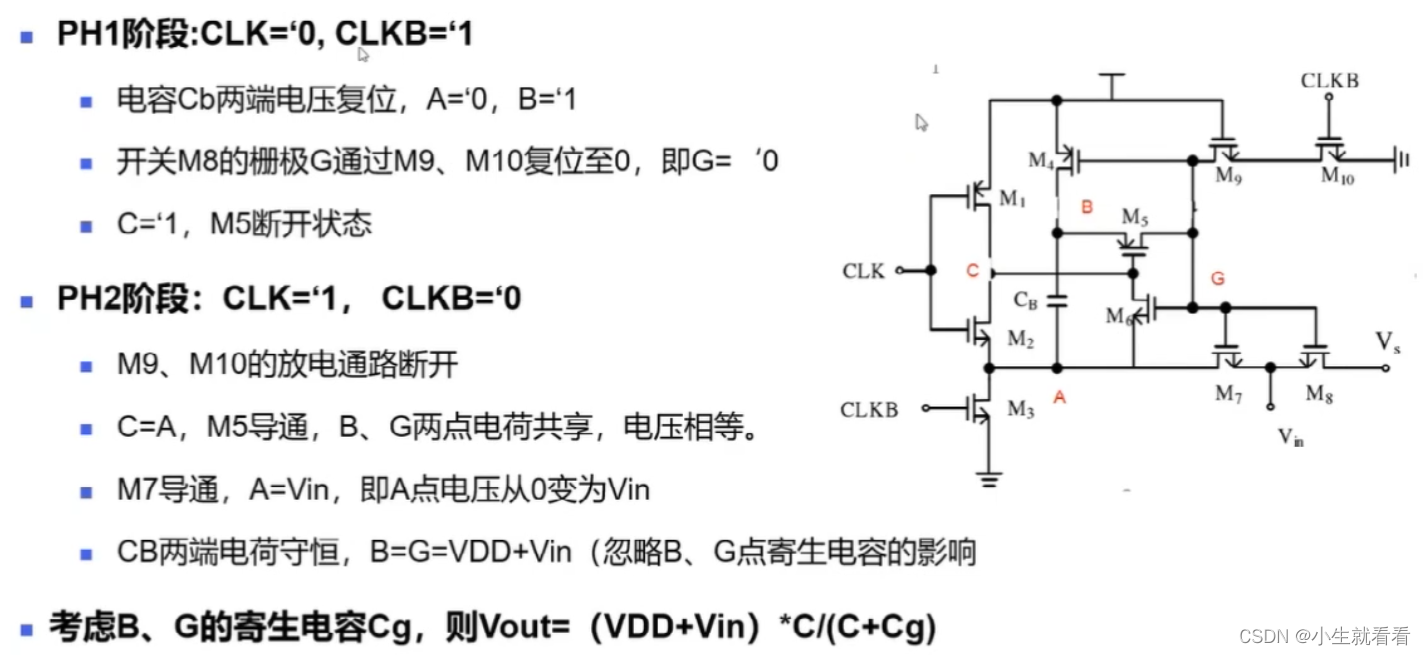

栅压自举开关实现:

- CLK=0(复位阶段):M3导通,A点下拉到 0;M9和M10导通,G点下拉到0;栅极电压为0,M6、M7和M8都断开;此时M4导通,B点上拉到VDD;而C点也为VDD,M5也是断开。

- CLK=1(自举阶段):M10断开,电容上级板放电通路掐断。M3断开而M2导通,(C点原来为VDD,A点为0),C点被放电到0,M5导通,此时 B和G 点电荷共享,G上拉到VDD(可能略低一点);G上拉,M7导通,Vin传到A点,A点抬高到Vin,电荷守恒B点和G点抬高到VDD+Vin;

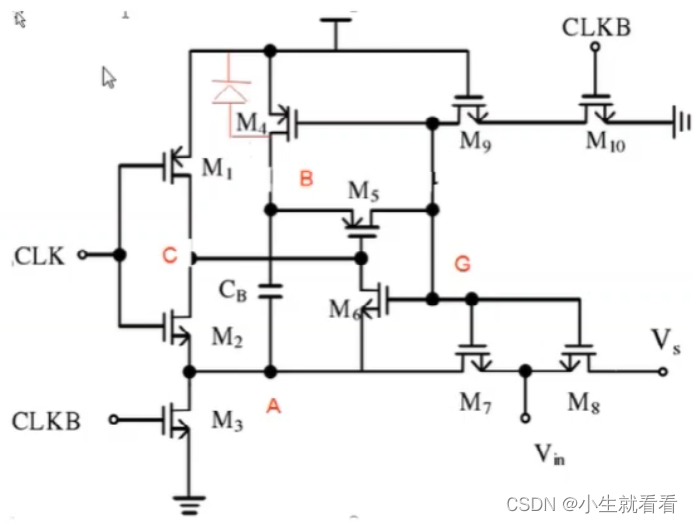

栅压自举开关实现(PMOS衬底连接):

如图,在自举阶段,如果M4和M5的衬底接在VDD,则会产生一个PMOS有源区和衬底之间的正向寄生二极管(有源区P型,衬底N阱),由于该二极管的存在,导致B点产生漏电,使得B点最高电压只能上升到 VDD+0.7V。(实际B点摆幅VDD~2VDD)。

因此,PMOS管 M4和M5 的衬底必须接到最高电位B点,保证B点能够达到高压。(从工艺器件角度,SD做出来都是一样的,哪个是SD看电压电流了)。

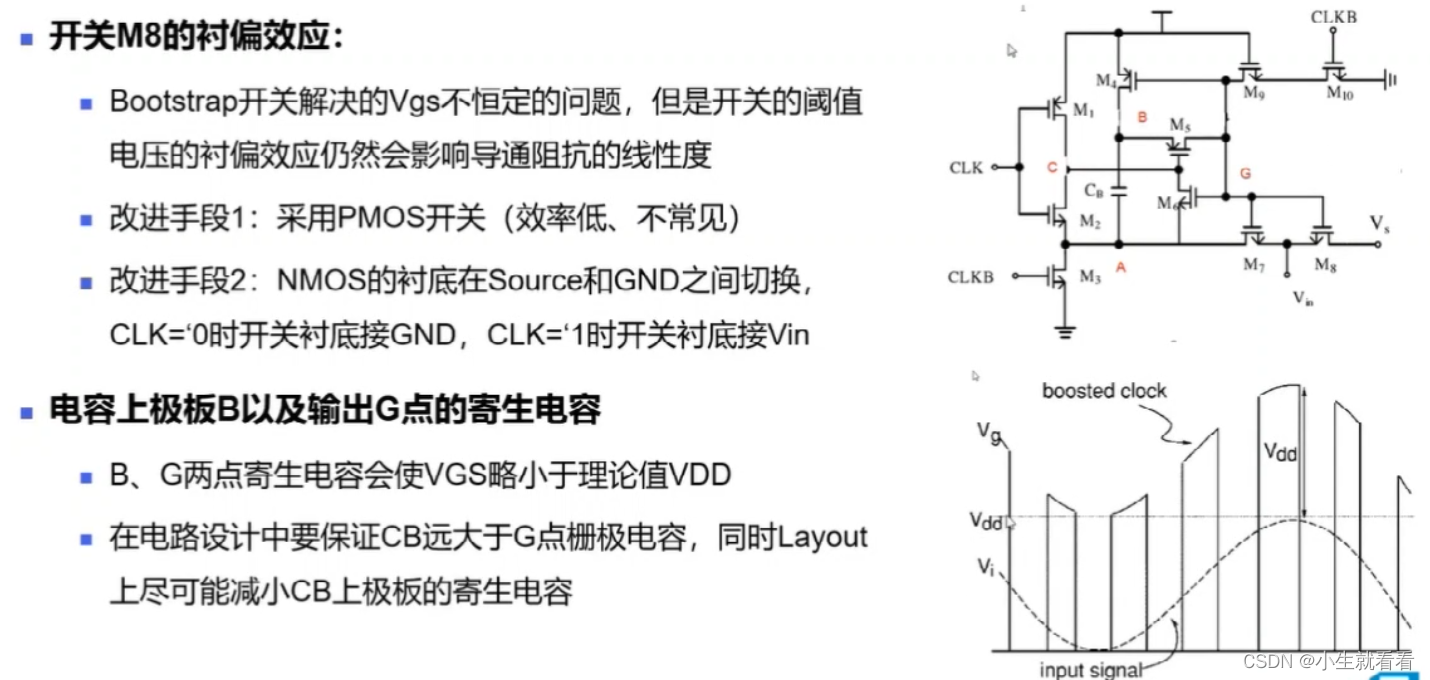

栅压自举开关非理想特性:

衬偏效应消除(要工艺支持!)

全摆幅范围内,Vth变化较大(能达到20%),会影响线性度!

方法一:更改开关结构,切换NMOS衬底连接。CLK=1,Sub=Vin;CLK=0,Sub=0。

代价:Req增加了 ,需要加大管子尺寸使得Req降低。

方法二:采用Low Vt器件减小Vth的值,减小Vth占比进而减小Vth影响。

代价:漏电可能比较严重,仔细观察各种corner下漏电情况,尤其是高温高速!

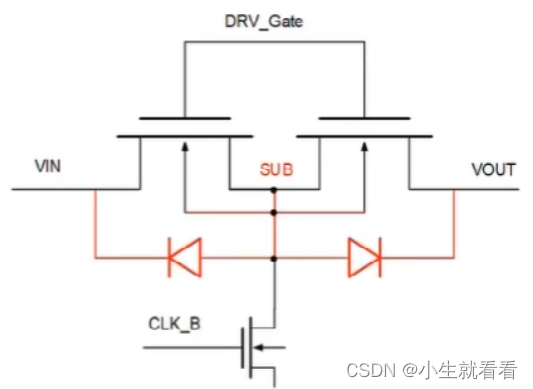

3-MOS开关结构:CLK=1:DRV_Gate = Vin+Vdd,两个MOS导通,Vin = Sub = Vout;

CLK=0:DRV_Gate = 0,两个MOS断开,Sub下拉到0。

PS:为什么开关管的衬底要切换,不能一直连在Vin上呢?

如图,在SUB和Vout之间存在寄生二极管,当Vin较高,而Vout(连在CDAC端)较低,寄生二极管会导通。故,采样之后衬底要接回0。

---------更新-----------

开关管衬底连接:到A点,这样,当CLK=0时,sub接0,CLK=1时,sub接Vin,确保采样不会漏电。

这篇关于SAR ADC系列7:采样开关种类(2023.7.31更新版)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!