本文主要是介绍FPGA通过移位相加实现无符号乘法器(参数化,封装成IP可直接调用),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

- 1.前言

- 2.原理

- 3.移位无符号乘法器实现,并参数化

微信公众号获取更多FPGA相关源码:

1.前言

在硬件设计中,乘法器是非常重要的一个器件,乘法器的种类繁多,常见的有并行乘法器、移位相加乘法器和查找表乘法器。

并行乘法器的实现非常简单,在Verilog中只需要通过 * 实现,若要进行有符号的乘法,需使用 系统函数$signed。

查找表乘法器实际上是先将乘法的计算结果提前算好,这样就可以在计算时通过查表的方式直接得到结果,一般用于位宽较小的情况。

移位相加乘法器是一种耗费较少资源的算法,其思想是将乘法转化为加法和移位运算,可以写成并行,也可以写成串行。串行的缺点是比较耗时,一般用于对性能要求不高的场合。并行的缺点是消耗资源多,但是可以一个周期就得结果。

2.原理

两个二进制数之间相乘,就是用乘数从最低位开始,每一位依次去和被乘数相乘,最终再将每一次所得的乘积相加,这样就得到了最终的乘积。但要注意的是,和十进制数的乘法类似,用乘数的某一位去和被乘数相乘时所得到的结果的最低位必须与该乘数所在位对齐,即每一步所得到的乘积应该依次左移移位,呈阶梯状排列。

(b)1 0 1 0x (a)1 1 0 1 ------------------0 0 0 0 1 0 1 0(i=1)0 0 0 0 0 0 0 0 (i=2) 0 0 0 0 1 0 1 0 (i=3)

+ 0 0 0 0 1 0 1 0 (i=4)

---------------------------0 0 0 1 0 0 0 0 0 1 0

以上面列的竖式计算,a=1010和b=1101相乘为例(均为无符号数)

- b的第0位为1,所以

result = result + b[0] * a<<0;

- b的第1位为0,result保持不变

result = result;

- b的第2位也为1,result进行累加

result = result + b[2] * a<<2;

- b的第3位为1,则得到最终的计算结果

result = result + b[3] * a<<3;

可以看到, W 位宽的无符号乘法器,如果使用串行移位相加,需要 W 个周期才能计算完成。搞懂原理之后,串行和并行的实现都非常简单。

3.移位无符号乘法器实现,并参数化

并行移位实现无符号乘法器RTL代码:

module my_Multipliers#(parameter WIDTH_A = 8,WIDTH_B = 8)

(input [WIDTH_A-1:0] a,input [WIDTH_B-1:0] b,output reg [WIDTH_A+WIDTH_B-1:0] out

);

integer i;

always @(a or b) beginout = 0;for(i=0; i<WIDTH_B; i=i+1)if(b[i])out = out + (a << i);

end

endmodule测试激励代码:

`timescale 1ns / 1ps

module my_Multipliers_tb;

reg [11:0] a ;

reg [15:0] b ;

wire [27:0] out ;

my_Multipliers

#(.WIDTH_A(12),

.WIDTH_B(16))

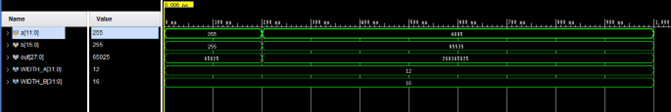

u1(.a (a),.b (b),.out(out));initial begina = 8'd255;//8bit最大值b = 8'd255;//计算结果应为65025#200a = 12'd4095;//12bit最大值b = 16'd65_535;//16bit最大值//计算结果应为268_365_825end

endmodule

如果要使用串行计算,稍微修改一下即可,比较简单,这里就不再赘述了,感谢趣的朋友可以自己去尝试实现。

微信公众号获取更多FPGA相关源码:

这篇关于FPGA通过移位相加实现无符号乘法器(参数化,封装成IP可直接调用)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!