本文主要是介绍HLS进阶技巧——反压fifo,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在Vitis HLS设计中,由于只能获取到fifo的empty、full信号,而不像RTL设计中还能拿到write/read count,所以在dataflow中,只能通过empty、full信号来进行数据驱动。反压fifo是通过fifo的full信号来控制程序的运行。下面介绍两种笔者涉及到的反压技巧,以便大家在自己的设计中举一反三。

技巧1

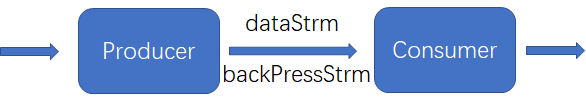

下图所示为dataflow中一个最基本的结构,在反压设计中,backPressStrm如果指定depth=2,那么Producer写入两个数后,如果Consumer没读取,则Producer会hang住等待Consumer中backPressStrm的读取,所以Consumer通过合理的控制实现了反压的应用。

伪码

{

#pragma HLS inline off

#pragma HLS dataflowhls::stream<bool> backPressStrm;

#pragma HLS stream variable = backPressStrm depth = 2hls::stream<DT> dataStrm; // DT 数据类型

#pragma HLS stream variable = dataStrm depth = N // N 按照实际需要Producer(backPressStrm, dataStrm );Consumer(backPressStrm, dataStrm );

}

技巧2

下图所示中,是一个Producer和多个Consumer的结构。

Producer每次写数据前,先通过none-blocking write (nb_write)的方式写backPressStrm,如果成功则将固定深度N的数据写入dataStrm中,否则直接返回进入下一个通路。可以实现任意数据量分配给Consumer模块。

Consumer则每次从dataStrm读取N个数后要读一次backPressStrm。

这篇关于HLS进阶技巧——反压fifo的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!