本文主要是介绍SDR SDRAM和DDR SDRAM的区别,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

SDR SDRAM(Single Data Rate Synchronous Dynamic Random Access Memory)和DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)是两种不同类型的内存技术,它们的主要区别在于数据传输速率和工作原理,具体如下:

-

数据传输速率:

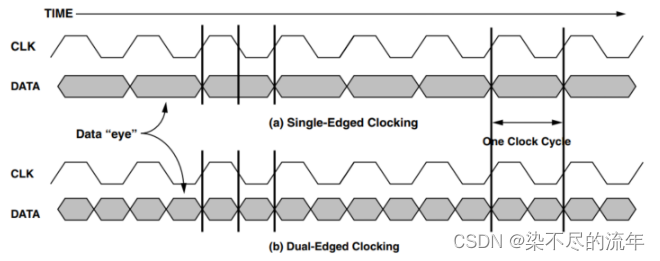

- SDR SDRAM:只能在时钟信号的上升沿传输数据,即单沿读写。

- DDR SDRAM:能够在时钟信号的上升沿和下降沿都进行数据传输,实现双倍数据速率。

-

带宽效率:

- 由于DDR SDRAM利用了时钟的两个边沿,所以在相同的时钟频率下,其数据传输速率是SDR SDRAM的两倍。例如,若SDR SDRAM运行在133MHz频率,其最大数据传输速率为133MT/s(百万次传输/秒),而DDR SDRAM在同样的时钟频率下,可以达到266MT/s。

-

引脚和接口:

- 物理接口不同,DDR SDRAM通常具有更多的引脚(如DDR1有184针),并且防呆口的位置与SDR SDRAM不同,两者不兼容。

- DDR SDRAM的电气接口也不同于SDR SDRAM,使用了SSTL2标准而非LVTTL。

-

命名和规格:

- SDR SDRAM命名通常基于时钟频率,如PC100(100MHz)或PC133(133MHz)。

- DDR SDRAM则以其数据传输速率命名,如PC2100(相当于DDR200,即在100MHz时钟下传输速率为200MT/s)。

-

内部结构和功能:

- DDR SDRAM可能采用预取技术(如2位预取),这意味着它在每个读取或写入周期中处理更多的数据位,进一步提高数据吞吐量。

- DDR SDRAM包含延时锁定环(DLL)技术,确保数据传输的精确时序,以及更复杂的电源管理功能。

-

数据采样方式DDR SDRAM有DQS

在SDR中,data eye是由两个同向时钟沿围成的(在图中即为在时钟上升沿,发送端驱动数据),中间还会有一个反向时钟沿,在该反向时钟沿的时刻(在图中即为下降沿)数据是稳定的,所以该反向时钟沿可以用来在接受端采样数据。简而言之就是每个data eye有两个可用时钟沿,左边的上升沿用于发送端驱动数据,中间的下降沿用于接收端采样数据,而右边的时钟沿就属于下一个data eye了。

而在DDR中,data eye是由紧邻的两个反相时钟沿围成,每个data eye可用的时钟沿个数减半(即只有一个),这个时钟沿只能用于驱动或采样数据,而无法把两件任务都完成。因此必须引入另一种机制来弥补这一缺陷,这一机制就是DQS(data strobe signal),它被称为同步时序参考信号( source-synchronous timing reference signal)。

另外,在高速接口设计中(尤其是DDR这种并行高速接口),要尽量减少信号传输时间的uncertainty(通常由skew和jitter两部分组成),以保证所有数据都能被同时正确采样,这就需要精细的板上布线和复杂的训练(traning)。为了减小时序收敛难度,DDR不是同时将所有DQ线的时序同时进行约束,而是将它们每8个bit为1组,且每一组都有自己的DQS信号。

-

发展和演进:

- SDR SDRAM是较早的技术,而DDR SDRAM是其后续发展。

这篇关于SDR SDRAM和DDR SDRAM的区别的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!