本文主要是介绍使用Vivado进行上板验证过程,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

环境介绍

2023.2版的vivado,是比较新的,弃用了之前三个黄色菱型的设计,采用的是AMD的图标。

Vivado v2023.2 (64-bit)

SW Build: 4029153 on Fri Oct 13 20:14:34 MDT 2023

IP Build: 4028589 on Sat Oct 14 00:45:43 MDT 2023

SharedData Build: 4025554 on Tue Oct 10 17:18:54 MDT 2023

第一步:编写设计文件

流程

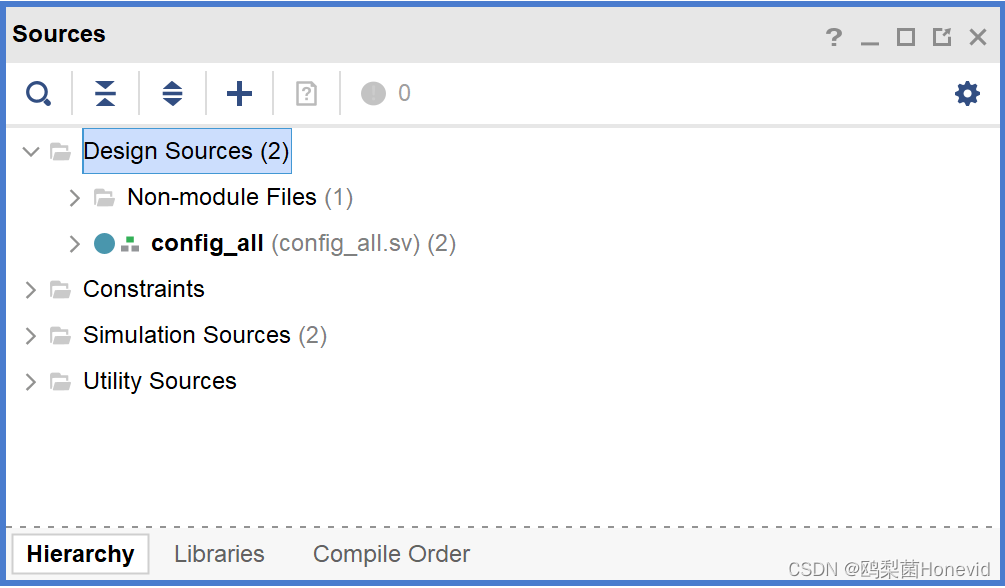

- 选中

source栏中的Design Source

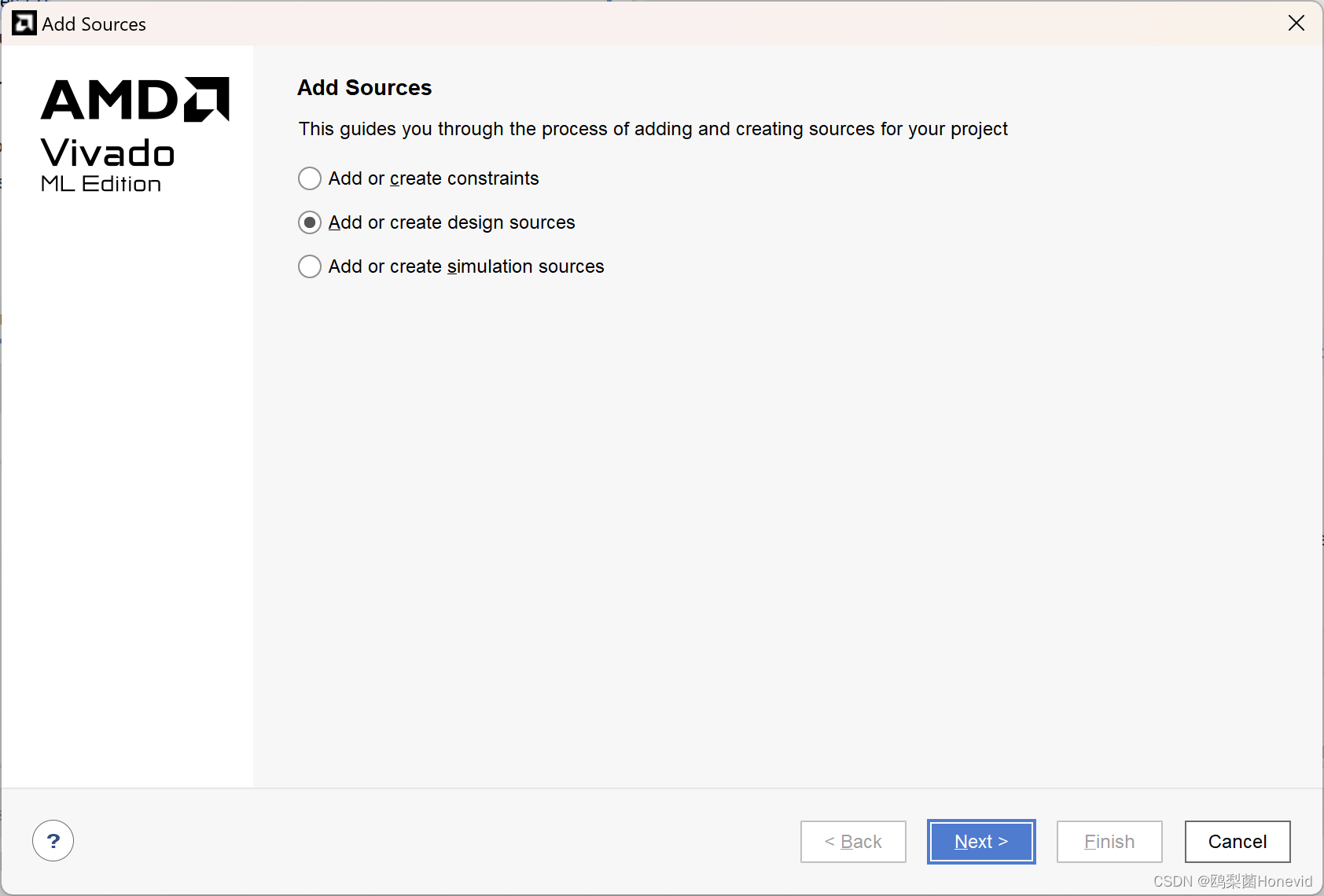

- 然后点击上面的

+号,添加design文件,点击next

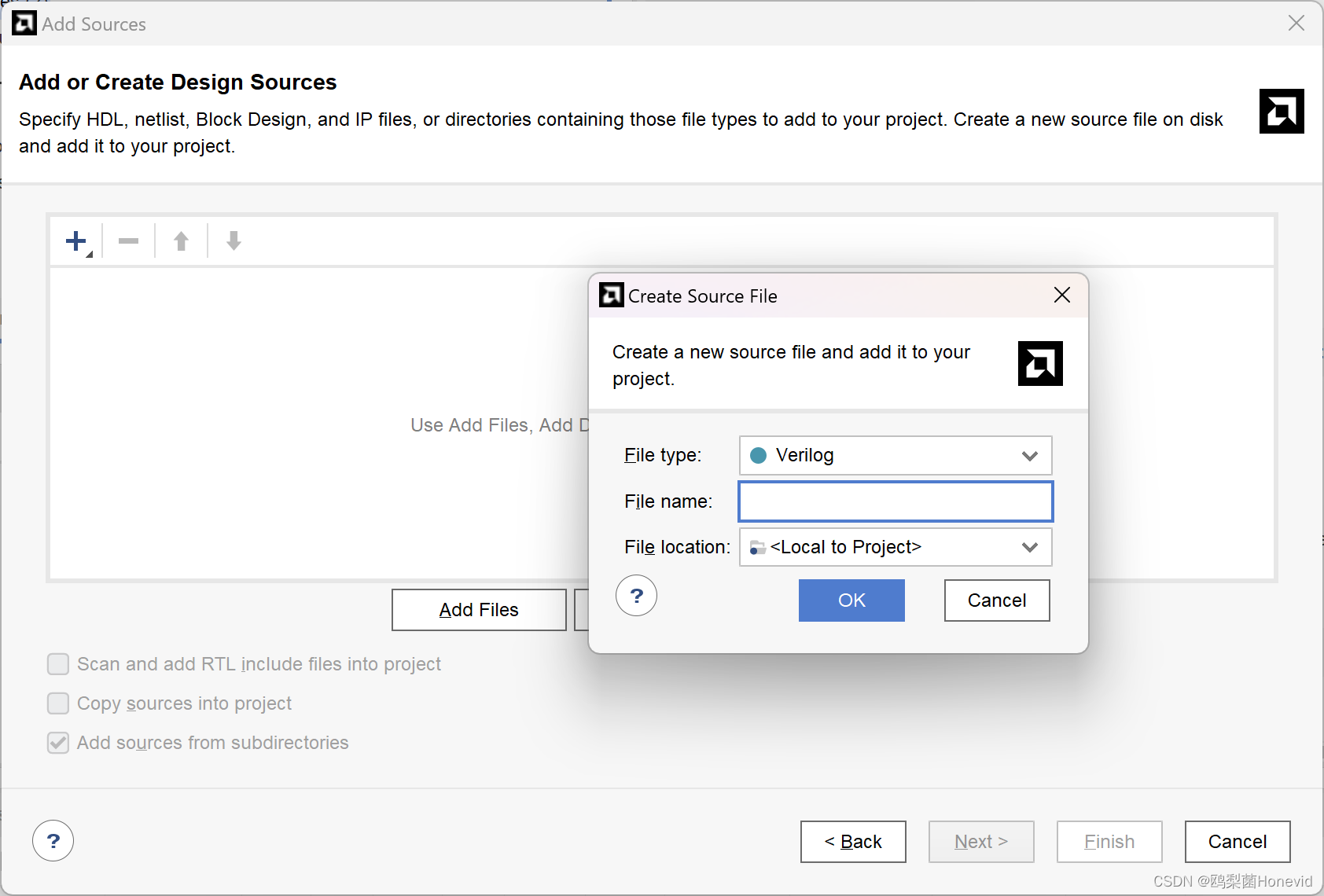

- 可以选择创建新的文件,或者选择其他文件夹的文件进行引用,下图是

creat file的效果

- 如果选择创建文件,需要自行编写模块,使用verilog语言或者system Verilog语言编程,如果对语法和格式要求有疑惑,可以参考我的专栏【Verilog】,相信你在读完所有文章后,可以快速掌握verilog语言的应用。

第二步 编写测试文件:testbench

testbench概述

Verilog的 TestBench其实是测试文件的意思。具体来说,Verilog测试基准(TestBench)是指用来测试一个Verilog实体的程序。它本身也由Verilog程序代码组成,用各种方法产生激励信号,通过元件例化语句以及端口映射将激励信号传送给被测试的Verilog设计实体,然后将输出信号波形写到文件中,或直接用波形浏览器观察输出波形。TestBench的主要目的是测试使用HDL设计的电路,对其进行仿真验证,以测试设计电路的功能、性能与设计预期是否相符。

在编写TestBench时,通常需要先产生一个模拟激励(波形),然后将这个激励加入到被测试模块中并观察其响应。接着,将输出响应与期望值进行比较,以验证设计的正确性。此外,TestBench还包含了一些关键组件,如时间表声明、模块定义、内部信号、被测试模块(UUT)的实例化、激励生成以及响应监控和比较等。

总的来说,Verilog的TestBench在硬件设计和验证过程中起到了至关重要的作用,它能够帮助工程师验证设计的正确性和性能,确保设计的电路能够按照预期工作。

流程

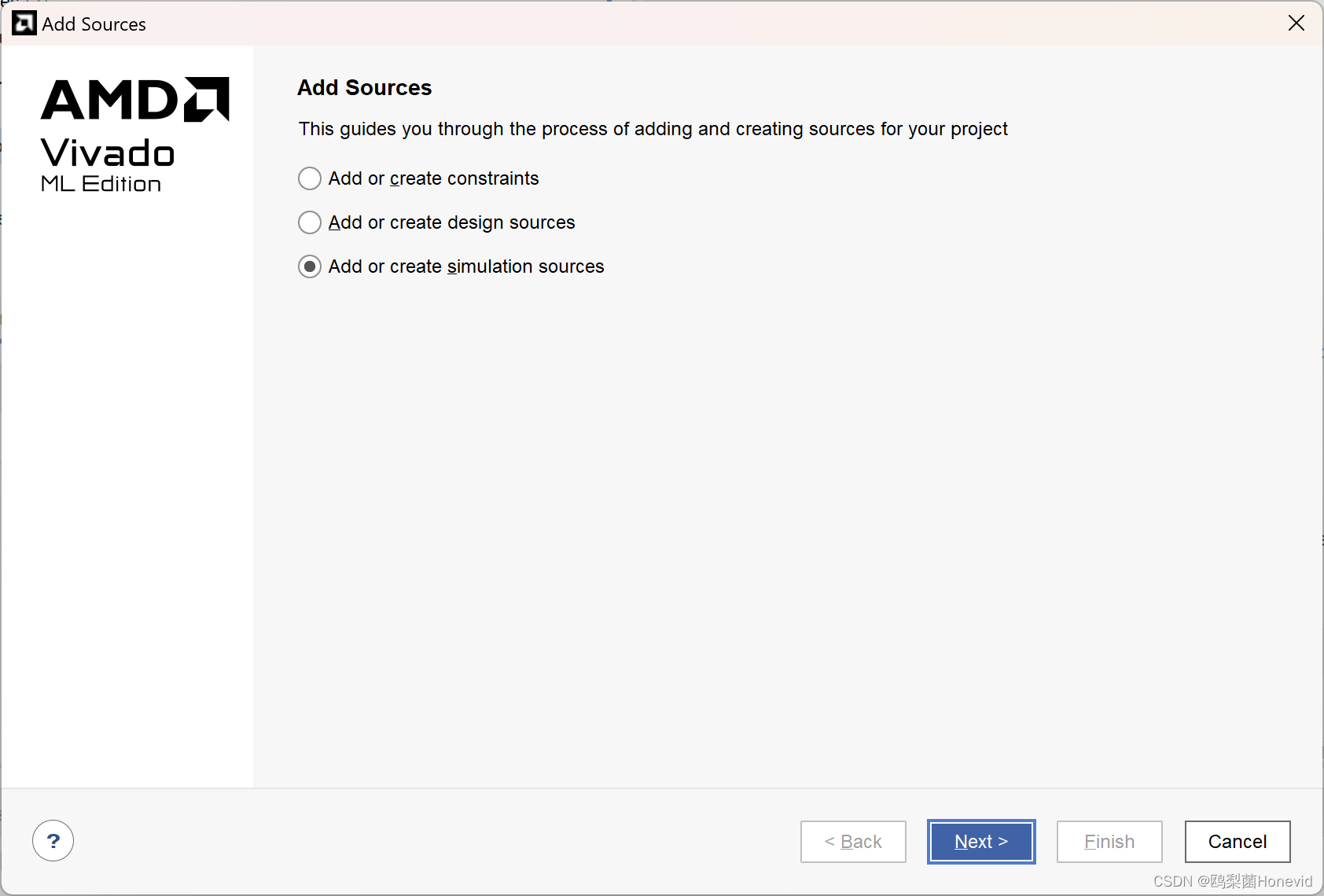

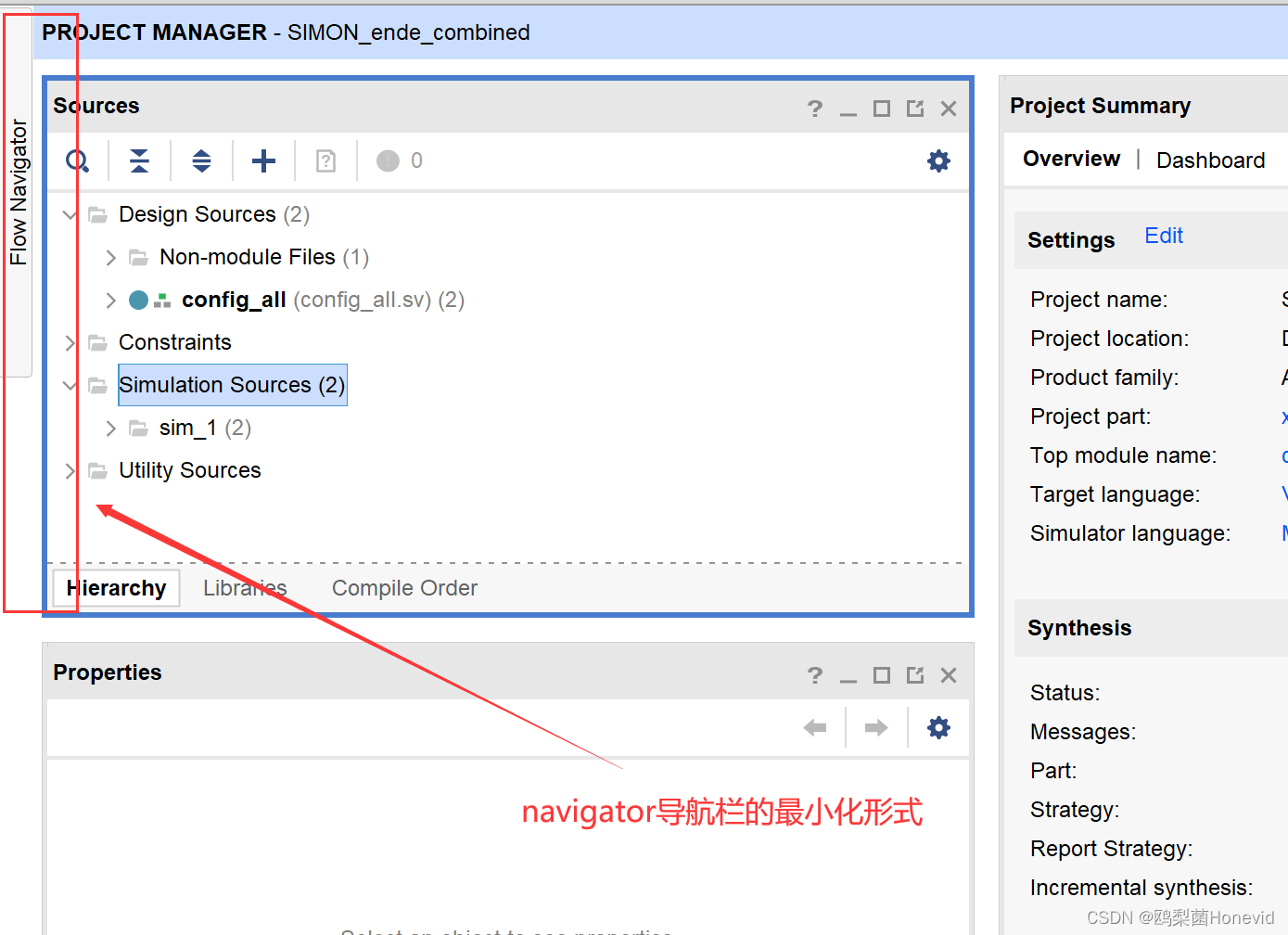

- 选中

source栏下的Simulation Sources文件夹

-

然后点击上面的

+号,添加simulation文件,点击next

-

接下来的编写过程与第一步差不多,可以参考第一步的内容

-

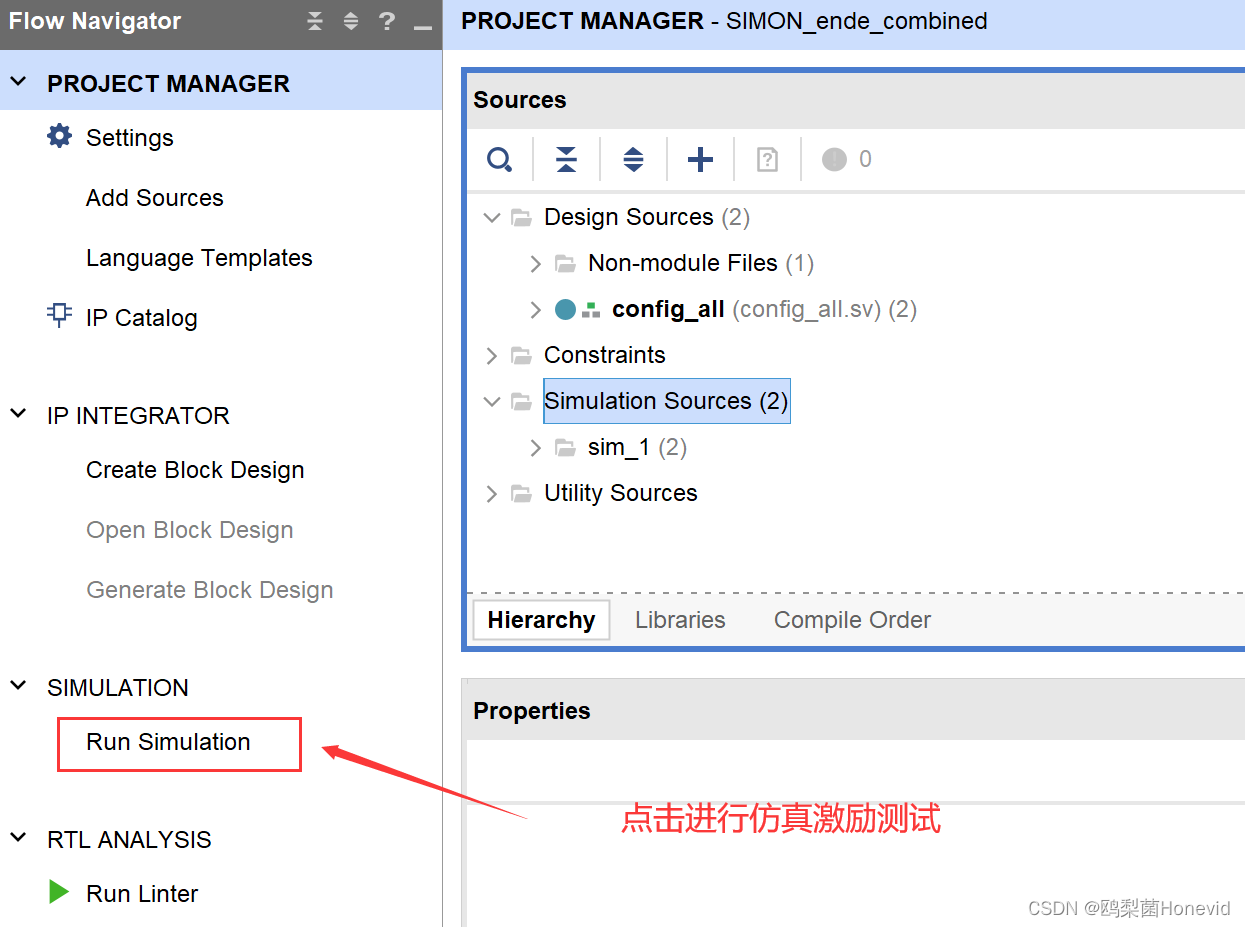

测试文件编写完毕,点击左侧

navigator导航栏simulation下的run simulation选项,进行激励测试:

-

如果激励测试得到的波形图符合预期效果,就可以接下去进行第三步了。

第三步:综合Synthesis

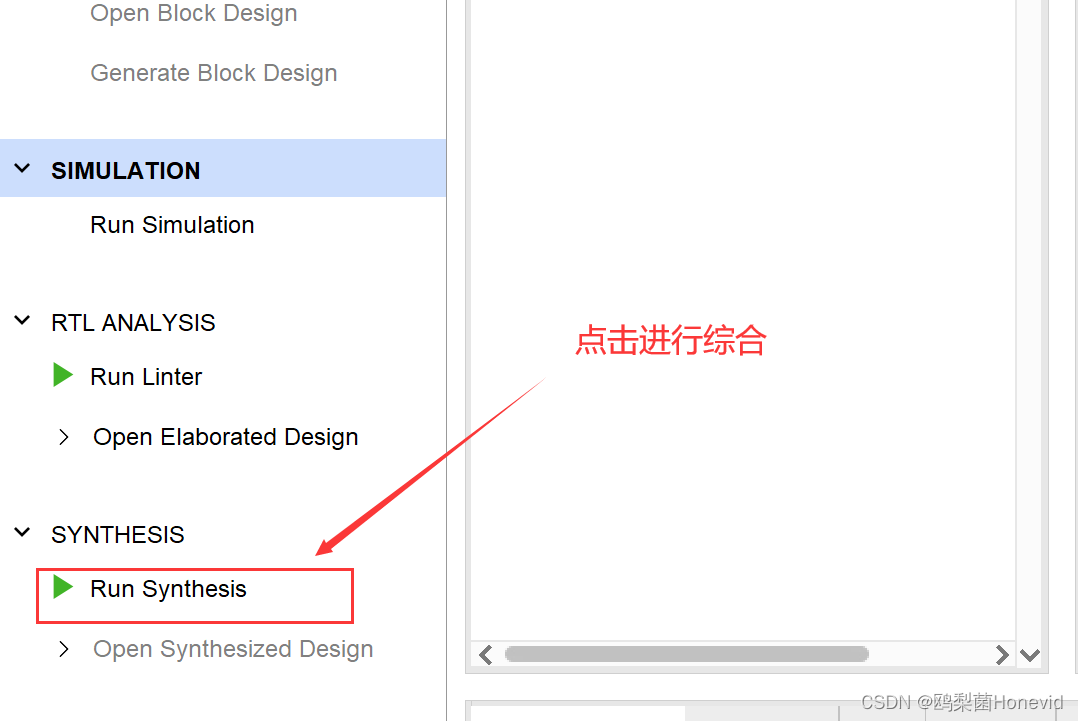

- 在进行

run simulation的选项下方找到run synthesis进行综合

- 综合过程中,程序右上角会出现综合进展的提示,等待进行,尽量不要点击取消,如果完成,会提示

synthesis complete

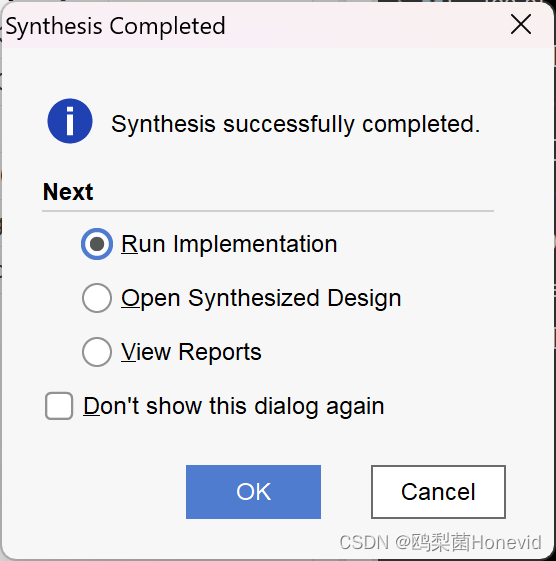

- 同时会弹出

synthesis successfully completed提示弹窗,弹窗上面有三个选项,由上到下是我们接下来需要进行的流程,因此不需要选择,直接点击ok

第四步 执行 implementation

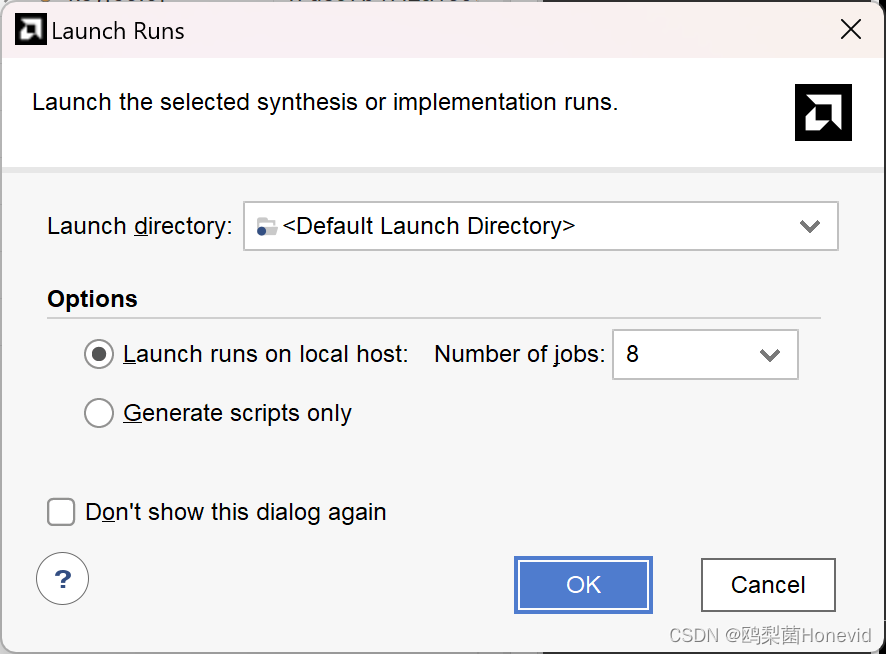

- 接下来是设置引脚,出现下面的弹窗点击

ok

- 右上角提示进展

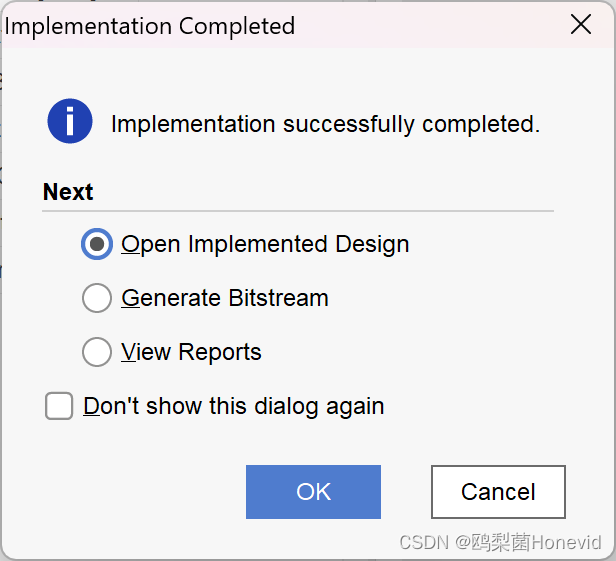

- 执行完毕会出现弹窗,点击

ok

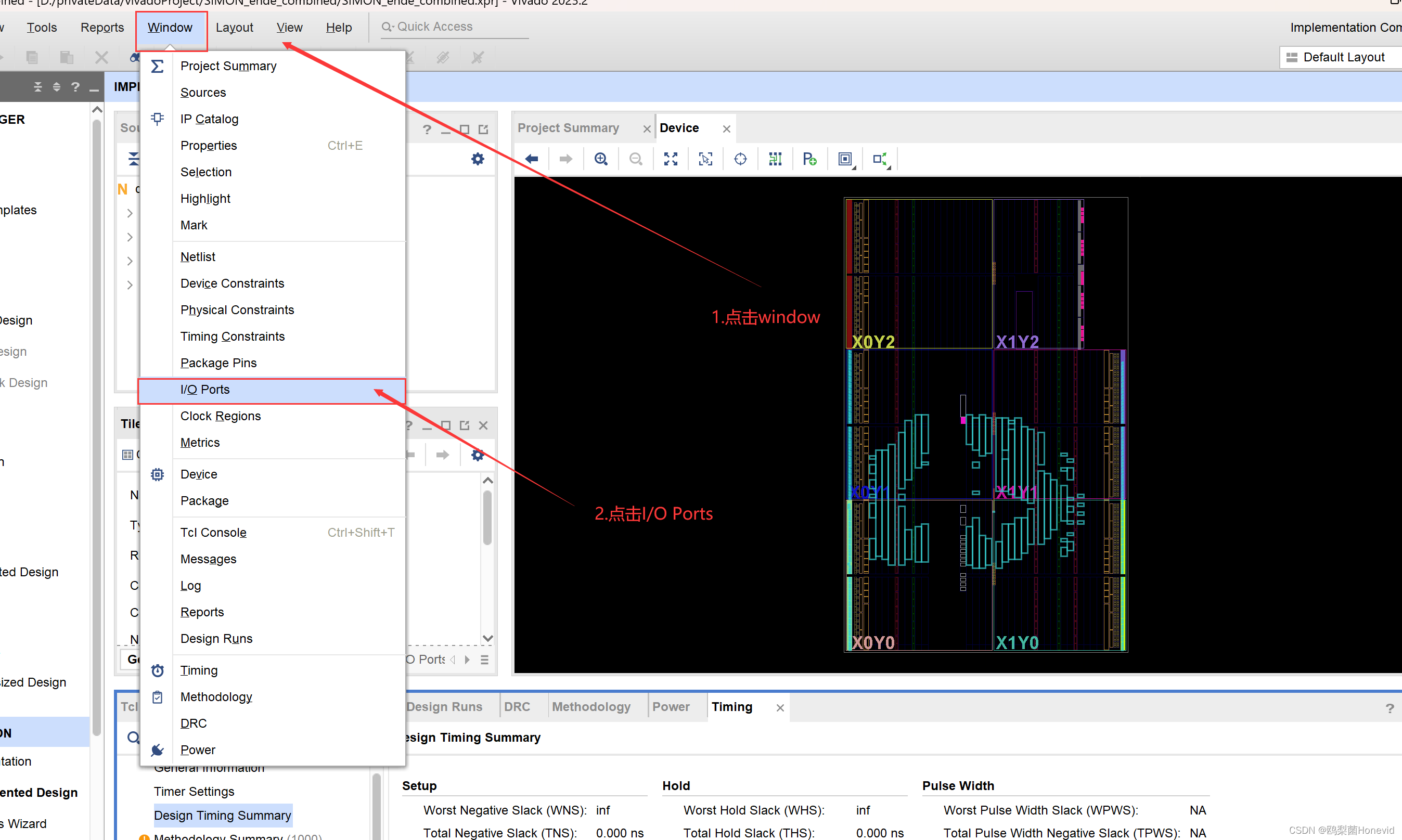

- 打开顶部导航栏的

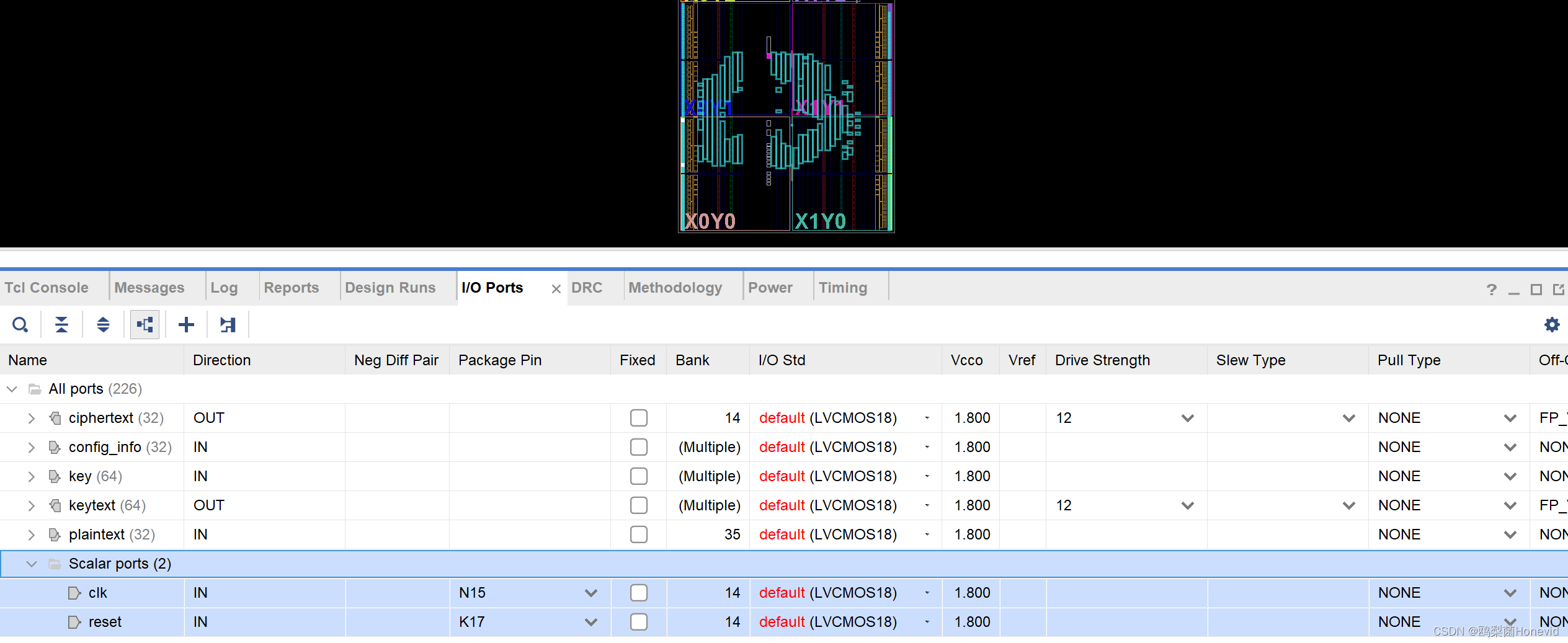

window项,点击I/O Port进入IO接脚配置

- 按照表格可以配置相应的接脚,具体接脚选择需要视FPGA开发板的实际情况来判断

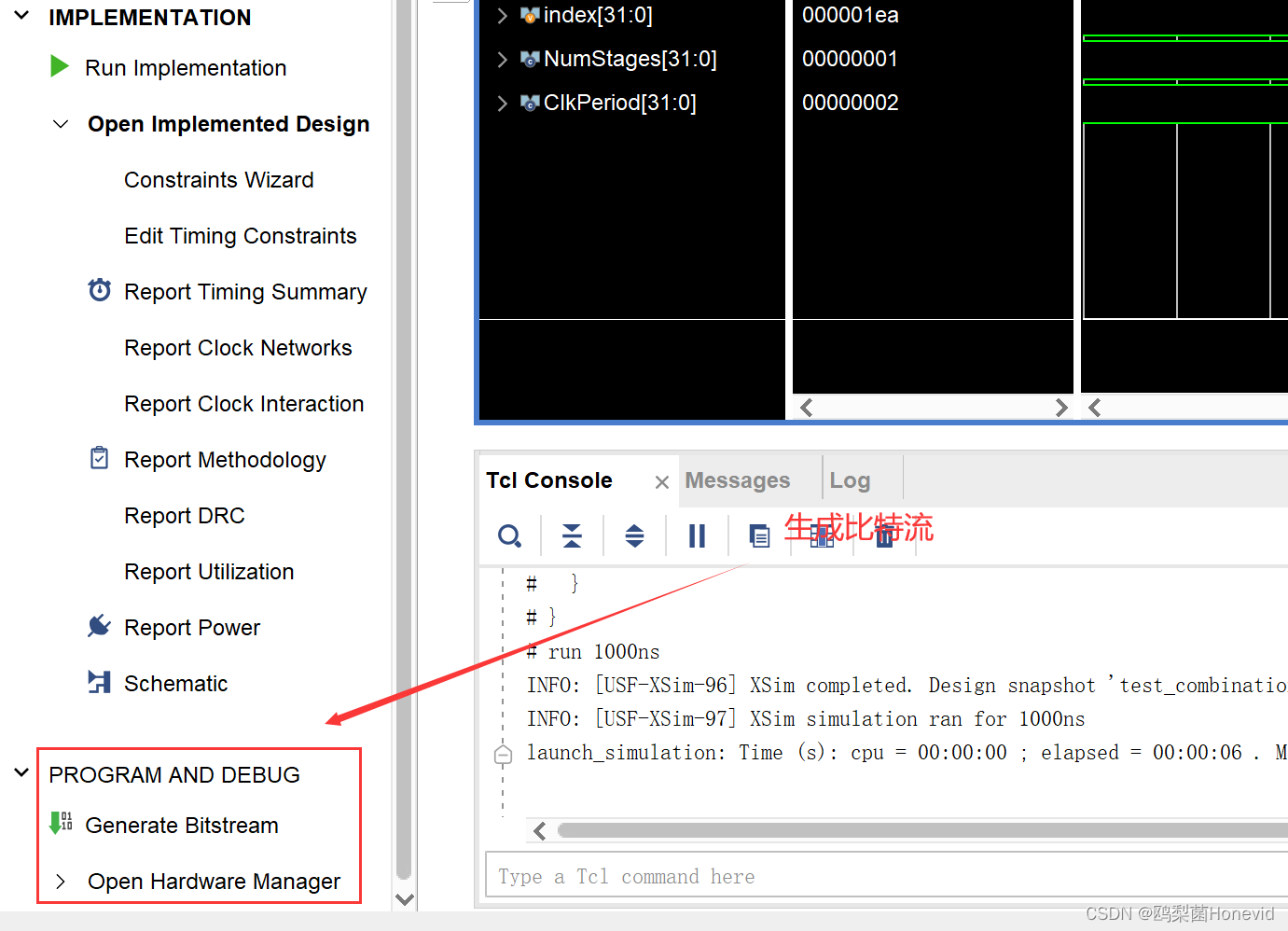

第五步:生成比特流

- 配置好接脚后,点击生成比特流

generate bitstream

- 比特流生成完毕,就是打开硬件管理器

open hardware manager,将电路上板验证

这篇关于使用Vivado进行上板验证过程的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!