本文主要是介绍根据状态转移图实现时序电路,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

描述

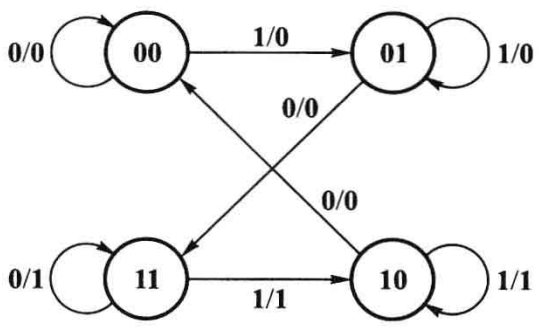

某同步时序电路的状态转换图如下,→上表示“C/Y”,圆圈内为现态,→指向次态。

请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

如图所示:

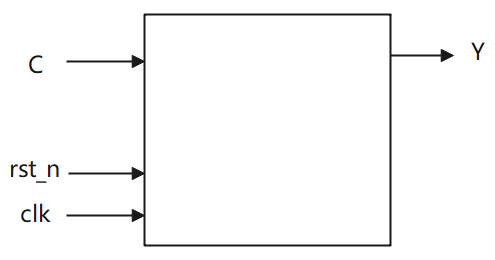

电路的接口如下图所示,C是单bit数据输入端。

如图所示:

输入描述

input C ,input clk ,input rst_n输出描述

output wire Y 解题分析

本题提供的是状态转换图,可采用状态机实现,也可采用列激励方程、输出方程,进而用D触发器和组合逻辑电路实现。本题解采用第二种方案实现。

由状态转换图可得出,电路共4个状态,所以使用2个寄存器来实现状态的寄存。两个寄存器的输出为Q1和Q0,两个寄存器的输入为D1和D0。可列出状态转换表如下:

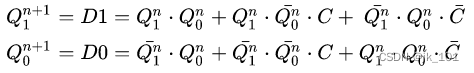

由状态转换表可列出激励方程如下:

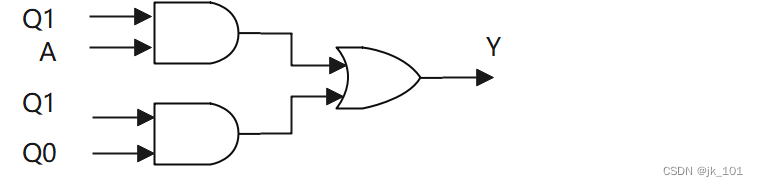

输出方程如下:

![]()

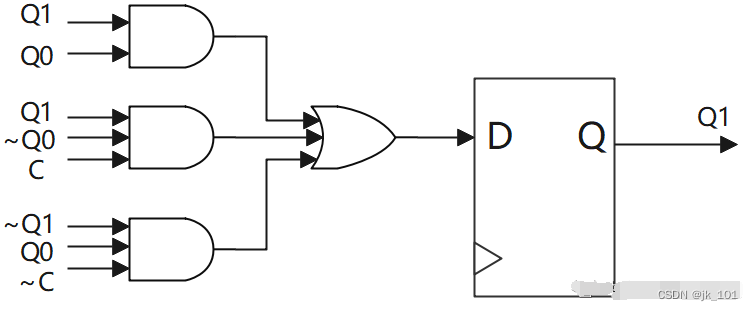

根据激励方程和输出方程以及思路整理,关键电路如下:

将电路转换成Verilog代码描述如下:

reg Q1 ;reg Q0 ;always @(posedge clk or negedge rst_n)beginif(!rst_n)Q1 <= 1'b0;elseQ1 <= (Q1 & (Q0 | C)) | (~Q1 & Q0 & ~C);endalways @(posedge clk or negedge rst_n)beginif(!rst_n)Q0 <= 1'b0;elseQ0 <= (~Q1 & (Q0 | C)) | (Q1 & Q0 & ~C);endassign Y = (C & Q1) | (Q1 & Q0);参考代码

`timescale 1ns/1nsmodule seq_circuit(input C ,input clk ,input rst_n,output wire Y

);reg Q1 ;

reg Q0 ;always @(posedge clk or negedge rst_n)beginif(!rst_n)Q1 <= 1'b0;else Q1 <= (Q1 & (Q0 | C)) | (~Q1 & Q0 & ~C);

end

always @(posedge clk or negedge rst_n)beginif(!rst_n)Q0 <= 1'b0;else Q0 <= (~Q1 & (Q0 | C)) | (Q1 & Q0 & ~C);

end assign Y = (C & Q1) | (Q1 & Q0); endmodule方法二

`timescale 1ns/1nsmodule seq_circuit(input C ,input clk ,input rst_n,output wire Y

);

reg [1:0] state;

always @(posedge clk or negedge rst_n)beginif(~rst_n)beginstate <= 2'b00;endelsebegincase(state)2'b00:beginif(C)state <= 2'b01;elsestate <= 2'b00;end2'b01:beginif(C)state <= 2'b01;elsestate <= 2'b11;end2'b10:beginif(C)state <= 2'b10;elsestate <= 2'b00;end2'b11:beginif(C)state <= 2'b10;else state <= 2'b11;endendcaseendendassign Y = (state == 2'b11)?1'b1:(state == 2'b10)?C:1'b0 ;

endmodule注:解题分析来源于网友,如有侵权,请告删之。

这篇关于根据状态转移图实现时序电路的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!