本文主要是介绍【ADF4351】使用FPGA进行SPI寄存器配置、使用FPGA计算各个频率的频点,ADF4351配置程序,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

简介

特性

输出频率范围:35 MHz至4,400 MHz

小数N分频频率合成器和整数N分频频率合成器

具有低相位噪声的VCO

可编程的1/2/4/8/16/32/64分频输出

典型抖动:0.3 ps rms

EVM(典型值,2.1 GHz): 0.4%

电源:3.0 V至3.6 V

逻辑兼容性: 1.8 V

可编程双模预分频器:4/5或8/9

可编程的输出功率

RF输出静音功能

三线式串行接口

模拟和数字锁定检测

在宽带宽内快速锁定模式

周跳减少

应用

无线基础设施(W-CDMA、TD-SCDMA、WiMAX、GSM、

PCS、DCS、DECT)

测试设备

无线局域网(LAN)、有线电视设备

时钟产生

简介

ADF4351结合外部环路滤波器和外部参考频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

ADF4351具有一个集成电压控制振荡器(VCO),其基波输出频率范围为2200 MHz至4400 MHz。此外,利用1/2/4/8/ 16/32/64分频电路,用户可以产生低至35 MHz的RF输出频率。对于要求隔离的应用,RF输出级可以实现静音。静音功能既可以通过引脚控制,也可以通过软件控制。同时提供辅助RF输出,且不用时可以关断。

所有片内寄存器均通过简单的三线式接口进行控制。该器件采用3.0 V至3.6 V电源供电,不用时可以关断。

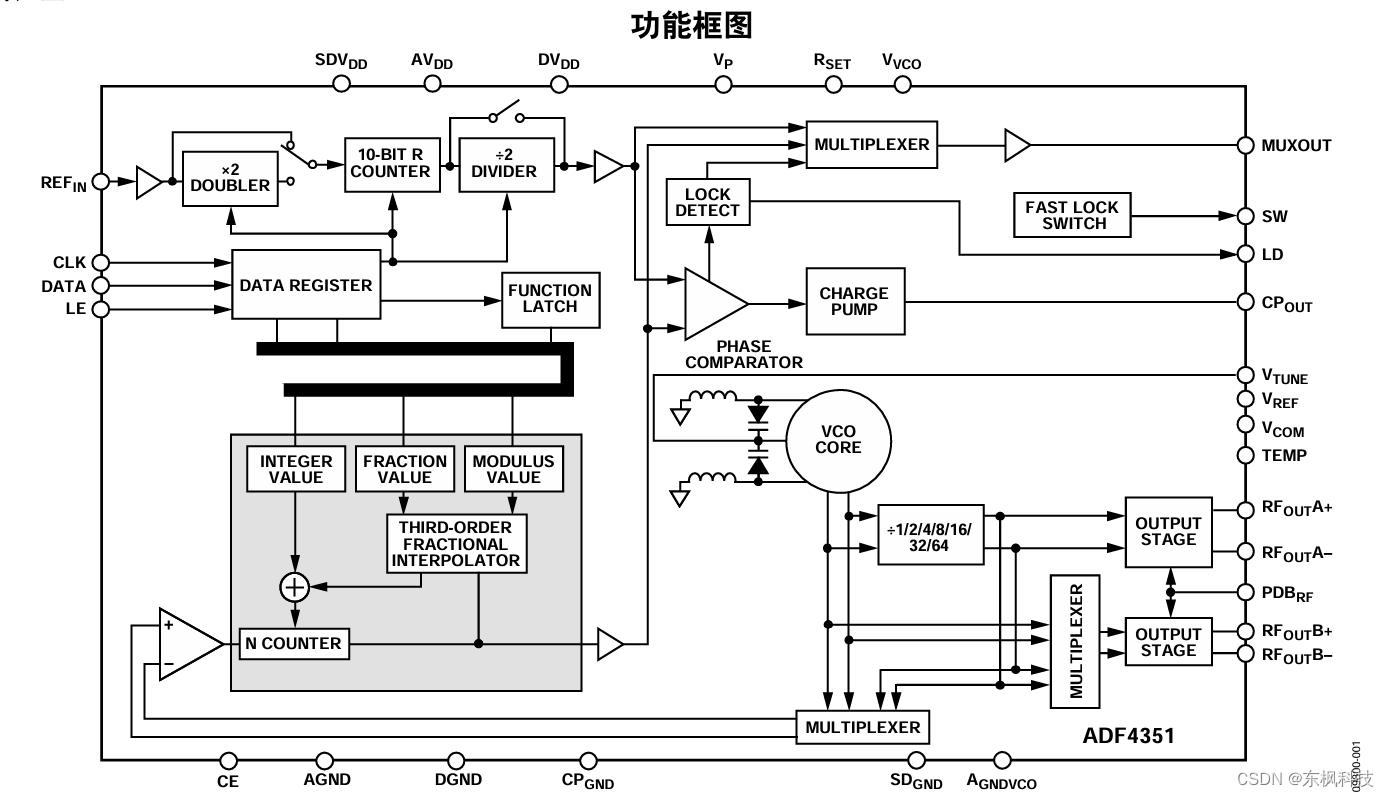

功能图

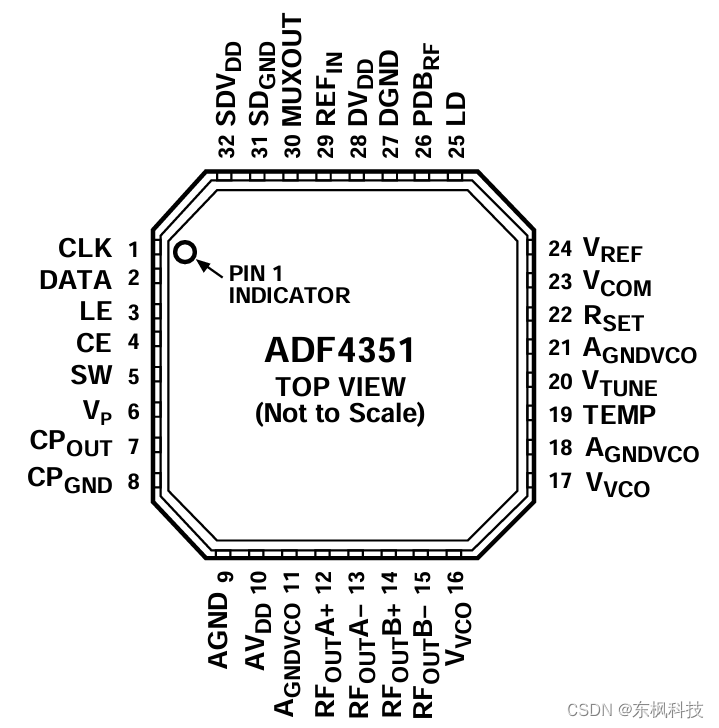

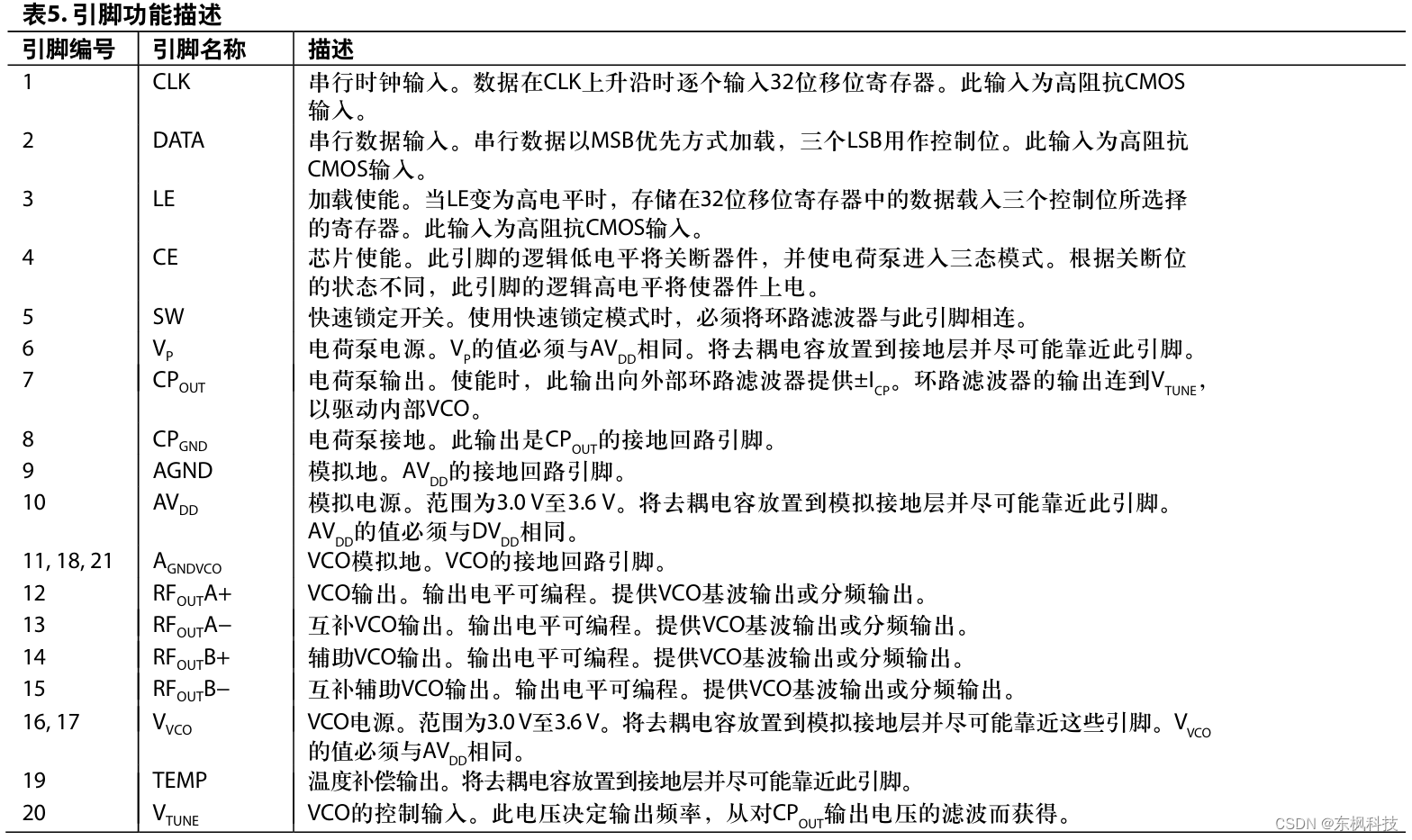

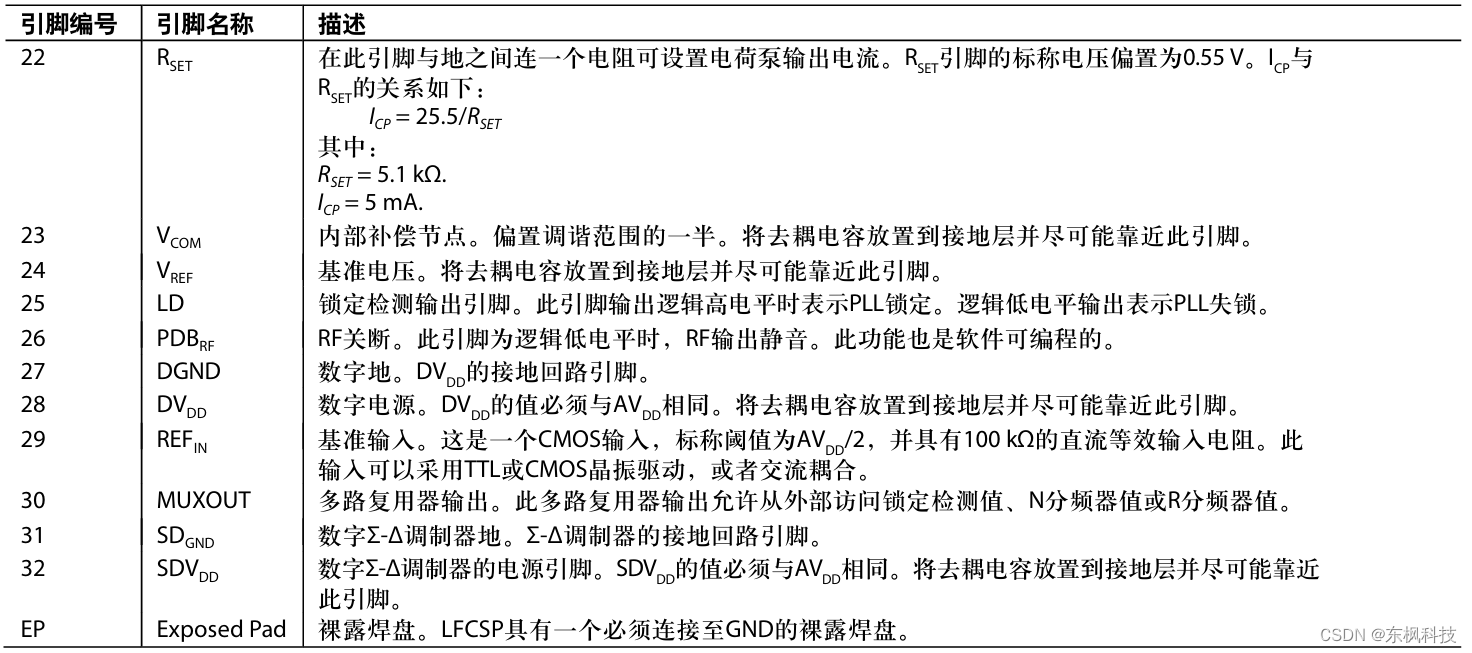

芯片引脚说明

芯片引脚图

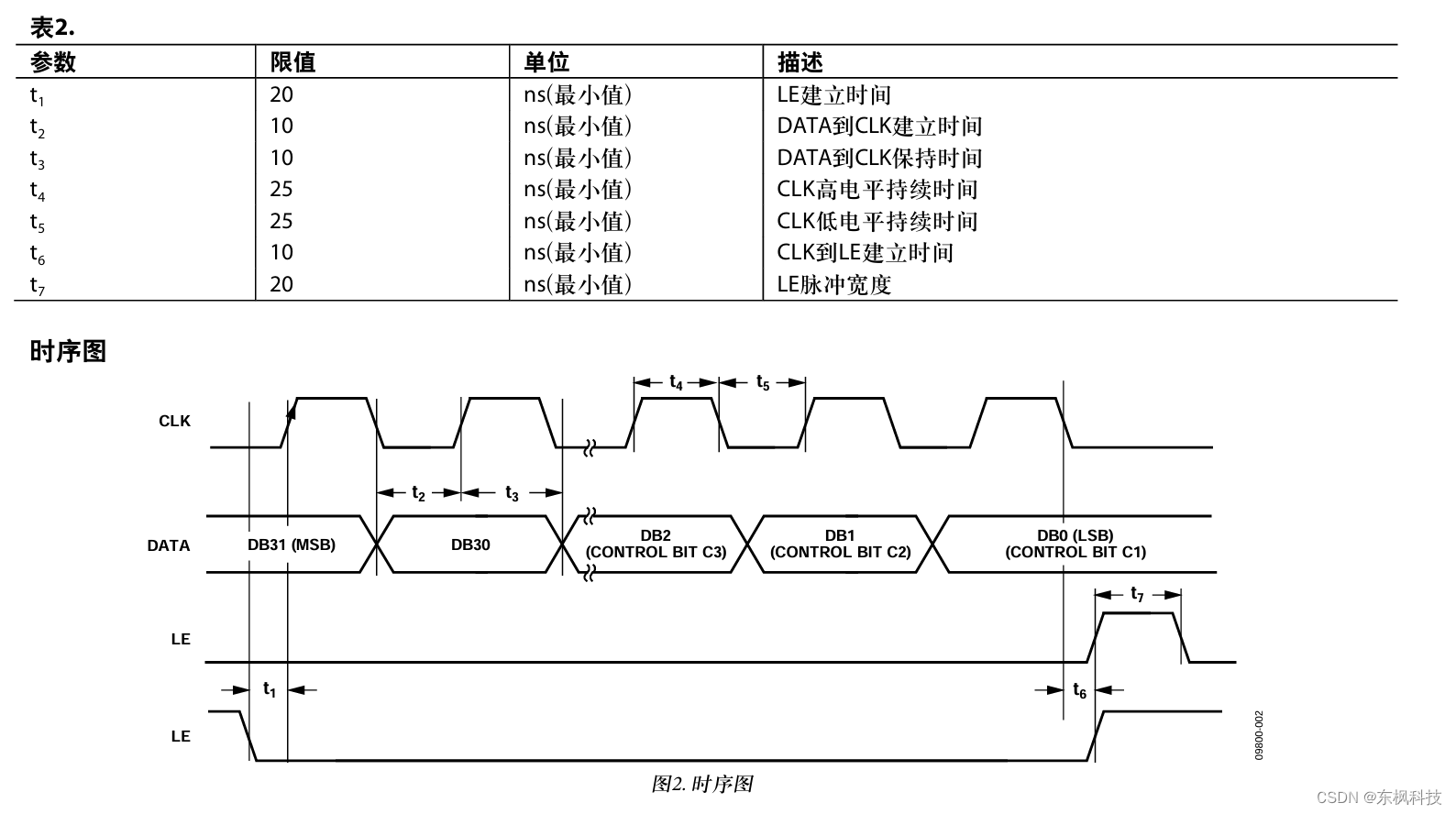

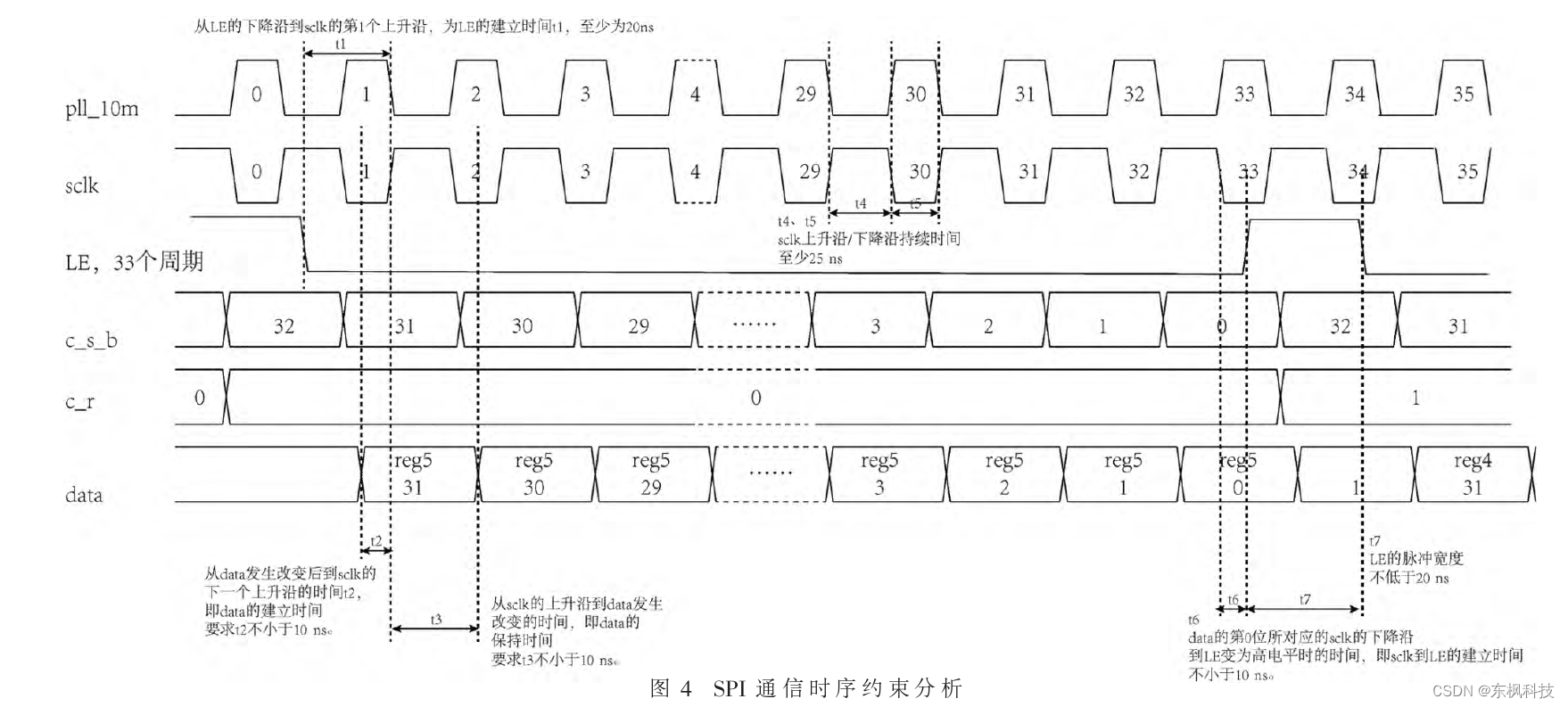

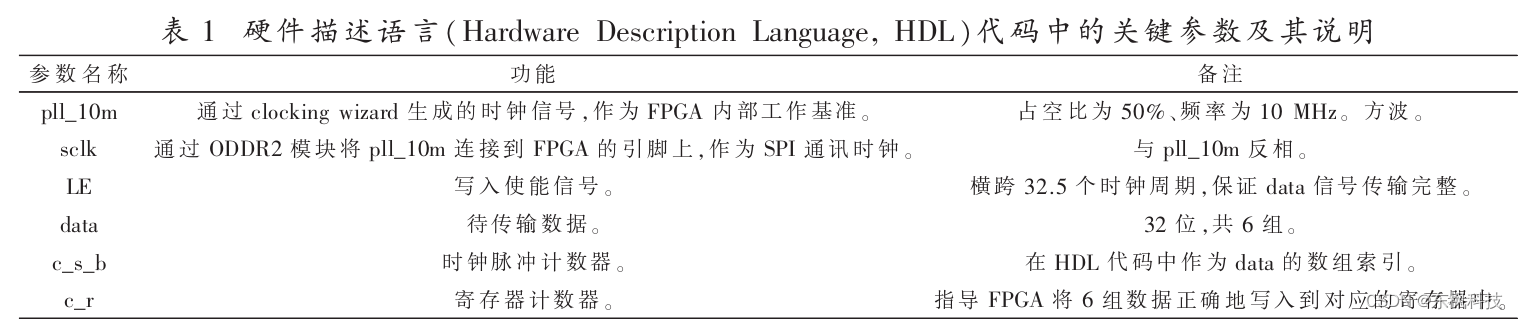

SPI 时序配置寄存器

module spi_adf4351(input wire clk, // 主时钟信号input wire reset, // 复位信号input wire [31:0] data_in, // 要发送的数据input wire start, // 开始发送信号output reg sclk, // SPI时钟output reg sdata, // SPI数据output reg enx, // SPI片选output reg done // 数据发送完成信号

);// 状态定义

localparam IDLE = 3'b000,START = 3'b001,SHIFT = 3'b010,WAIT = 3'b011,STOP = 3'b100;reg [2:0] state = IDLE; // 当前状态

reg [2:0] next_state; // 下一个状态

reg [31:0] shift_reg; // 移位寄存器

reg [5:0] bit_cnt; // 位计数器

reg [7:0] wait_cnt; // 等待计数器,用于产生延时always @(posedge clk or posedge reset) beginif (reset) beginstate <= IDLE;end else beginstate <= next_state;end

endalways @(state or start or bit_cnt or wait_cnt) begincase (state)IDLE: beginif (start) next_state = START;else next_state = IDLE;endSTART: beginnext_state = SHIFT;endSHIFT: beginif (bit_cnt == 32) next_state = STOP;else next_state = WAIT;endWAIT: beginif (wait_cnt == 100) next_state = SHIFT;else next_state = WAIT;endSTOP: beginnext_state = IDLE;enddefault: next_state = IDLE;endcase

endalways @(posedge clk) begincase (state)IDLE: beginsclk <= 0;enx <= 1;done <= 0;bit_cnt <= 0;wait_cnt <= 0;endSTART: beginshift_reg <= data_in;enx <= 0;endSHIFT: beginsdata <= shift_reg[31];shift_reg <= shift_reg << 1;sclk <= 1;bit_cnt <= bit_cnt + 1;wait_cnt <= 0;endWAIT: beginwait_cnt <= wait_cnt + 1;sclk <= 0;endSTOP: beginenx <= 1;done <= 1;endendcase

endendmodule测试

`timescale 1ns / 1nsmodule spi_adf4351_tb;reg clk_tb;

reg reset_tb;

reg start_tb;

reg [31:0] data_in_tb;

wire sclk_tb;

wire sdata_tb;

wire enx_tb;

wire done_tb;// 实例化spi_adf4351模块

spi_adf4351 DUT (.clk(clk_tb),.reset(reset_tb),.data_in(data_in_tb),.start(start_tb),.sclk(sclk_tb),.sdata(sdata_tb),.enx(enx_tb),.done(done_tb)

);// 生成时钟信号

initial beginclk_tb=0;forever #5 clk_tb=~clk_tb;// 假设系统时钟为100MHz

endinitial begindata_in_tb = 32'hA5A5A5A5; // 测试数据,可以根据需要修改reset_tb = 1;start_tb = 0;#20 reset_tb=0;#35 start_tb=1;#10 start_tb=0;

endendmodule频率FPGA 计算

原理

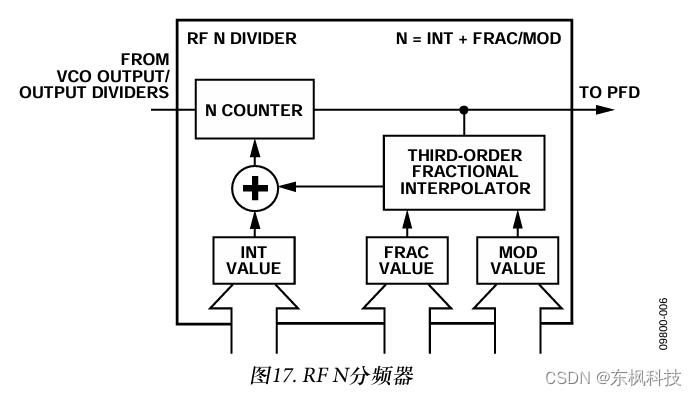

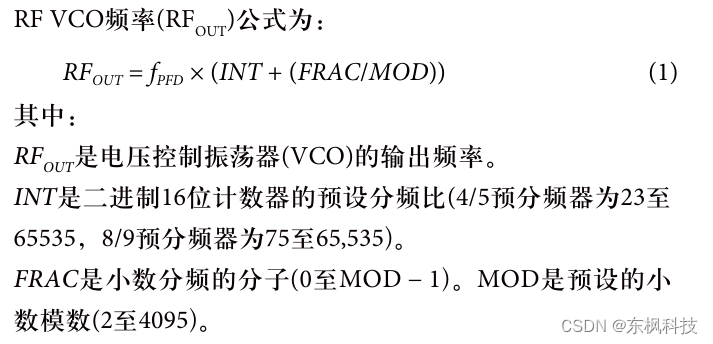

INT、FRAC、MOD与R分频器的关系

利用INT、FRAC和MOD的值以及R分频器,可以产生间隔为PFD频率的分数的输出频率。

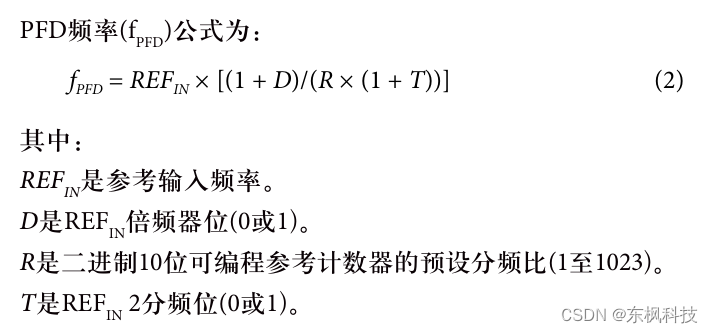

R分频器

利用10位R分频器,可以细分输入参考频率(REFIN)以产生PFD的参考时钟。分频比可以为1至1023。

寄存器映射

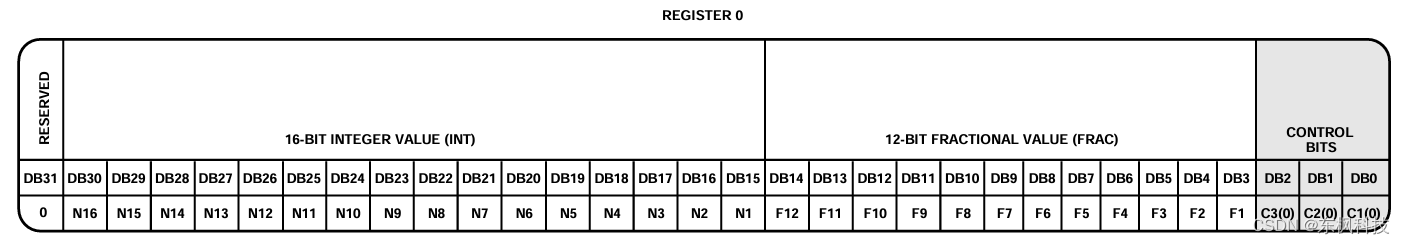

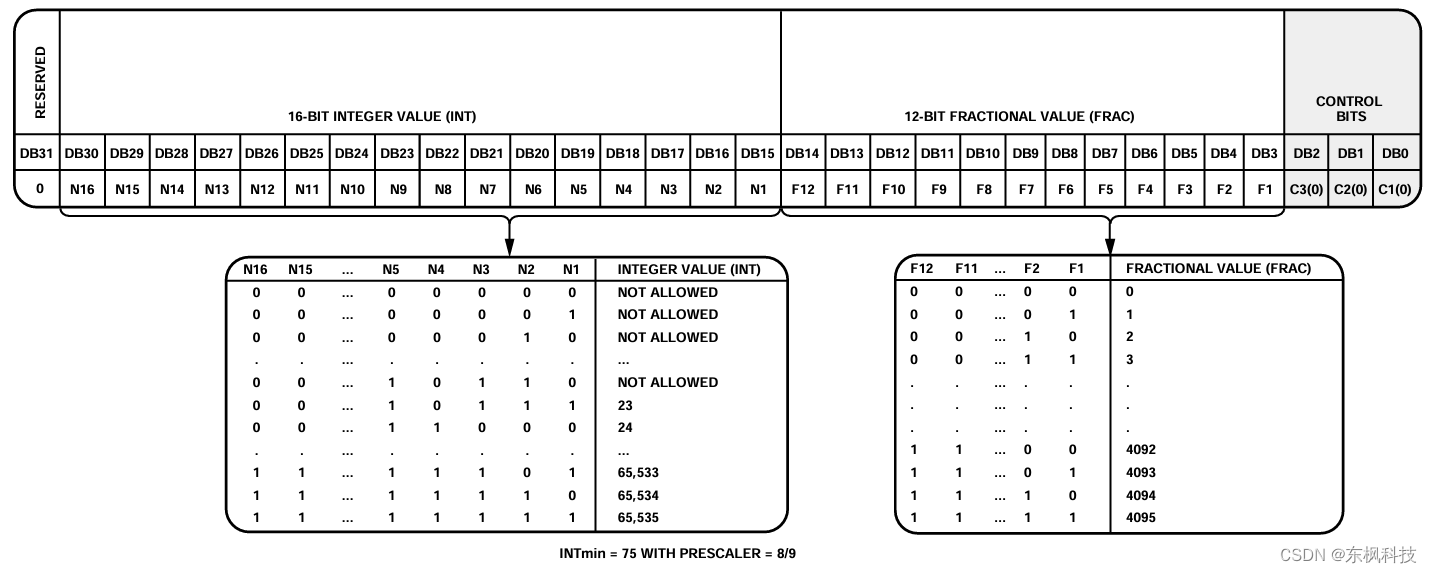

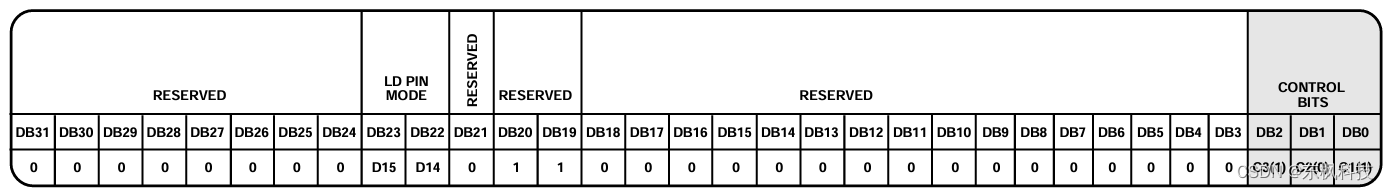

REGISTER 0

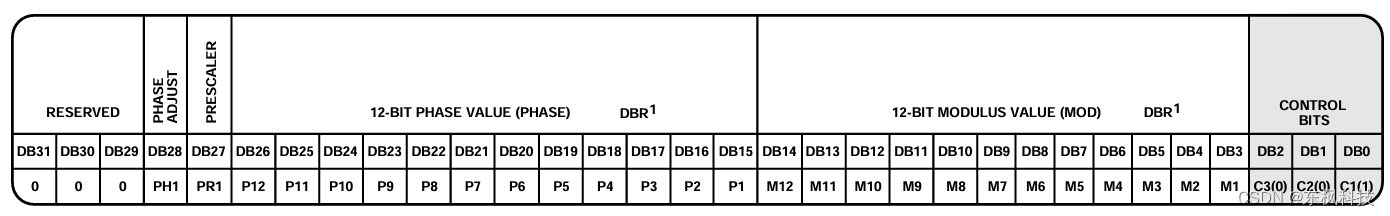

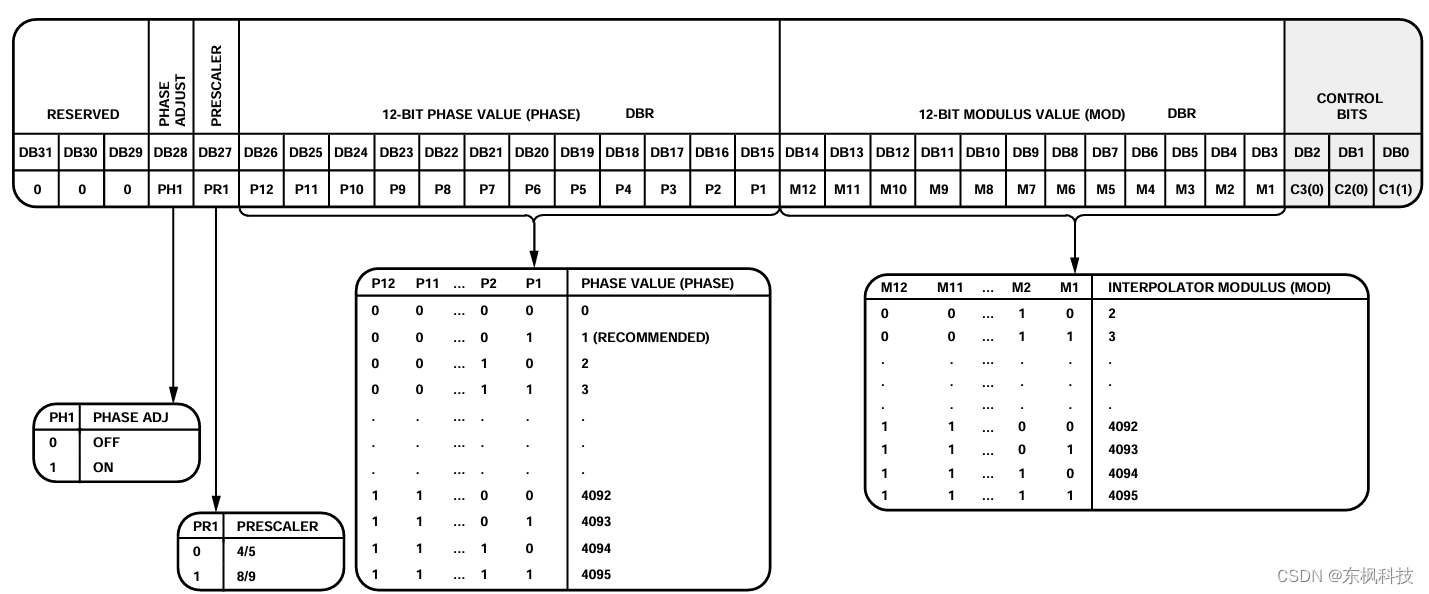

REGISTER 1

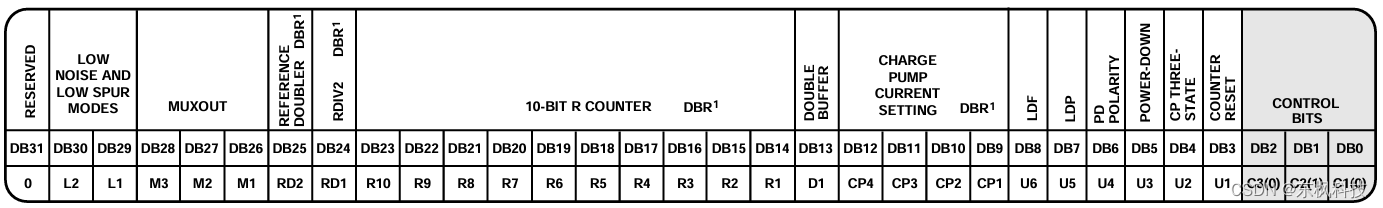

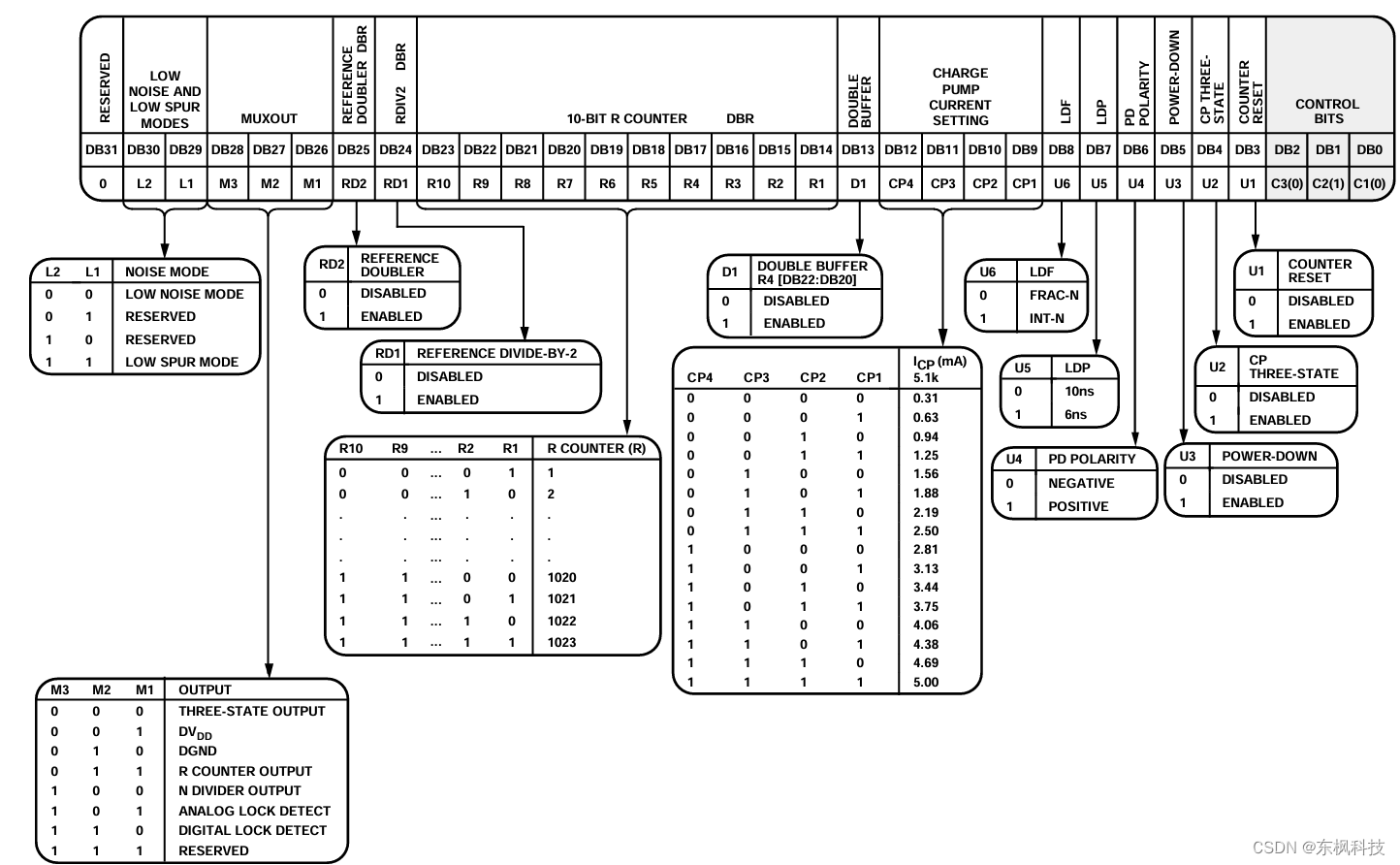

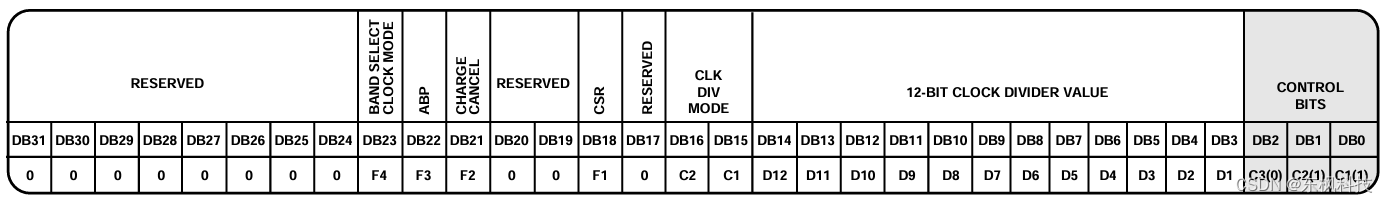

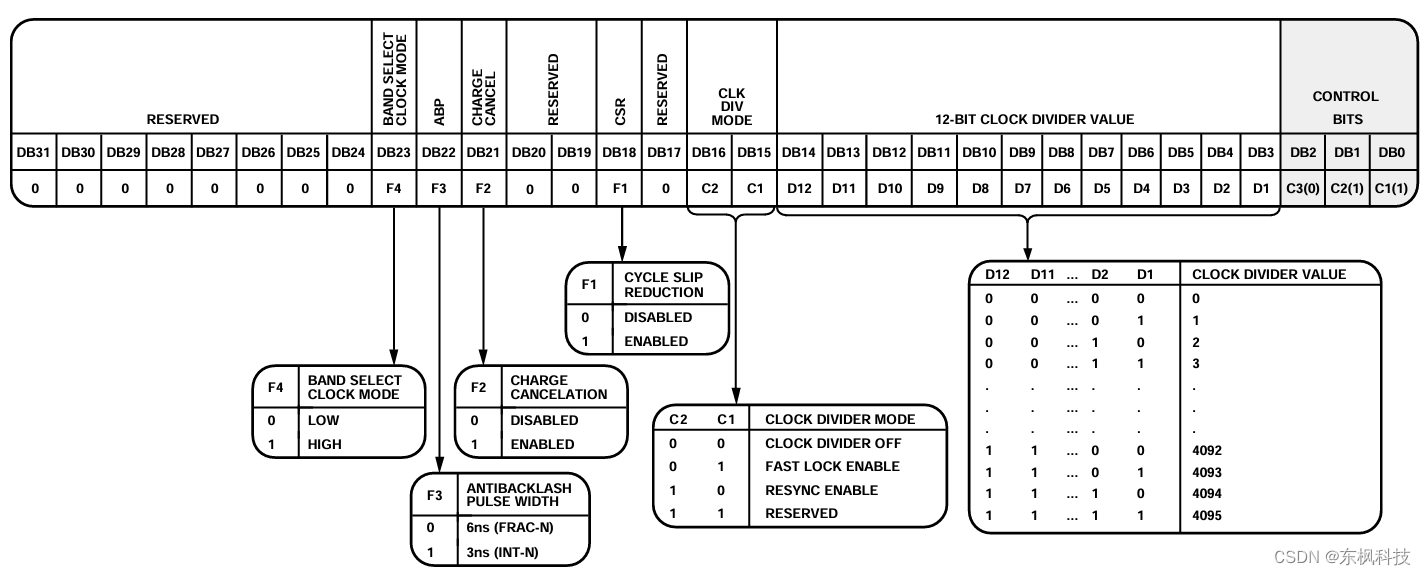

REGISTER 2

REGISTER 3

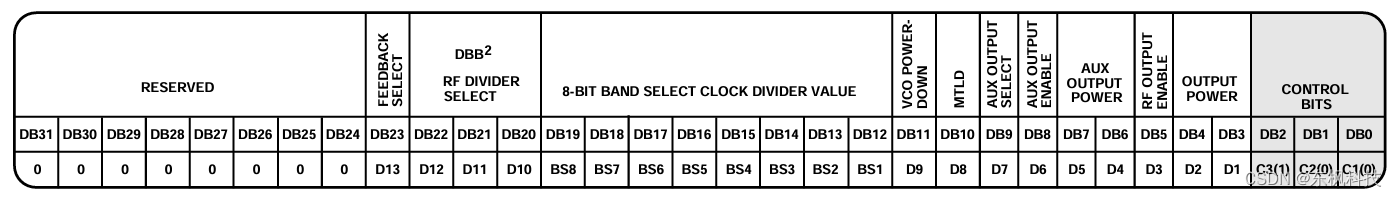

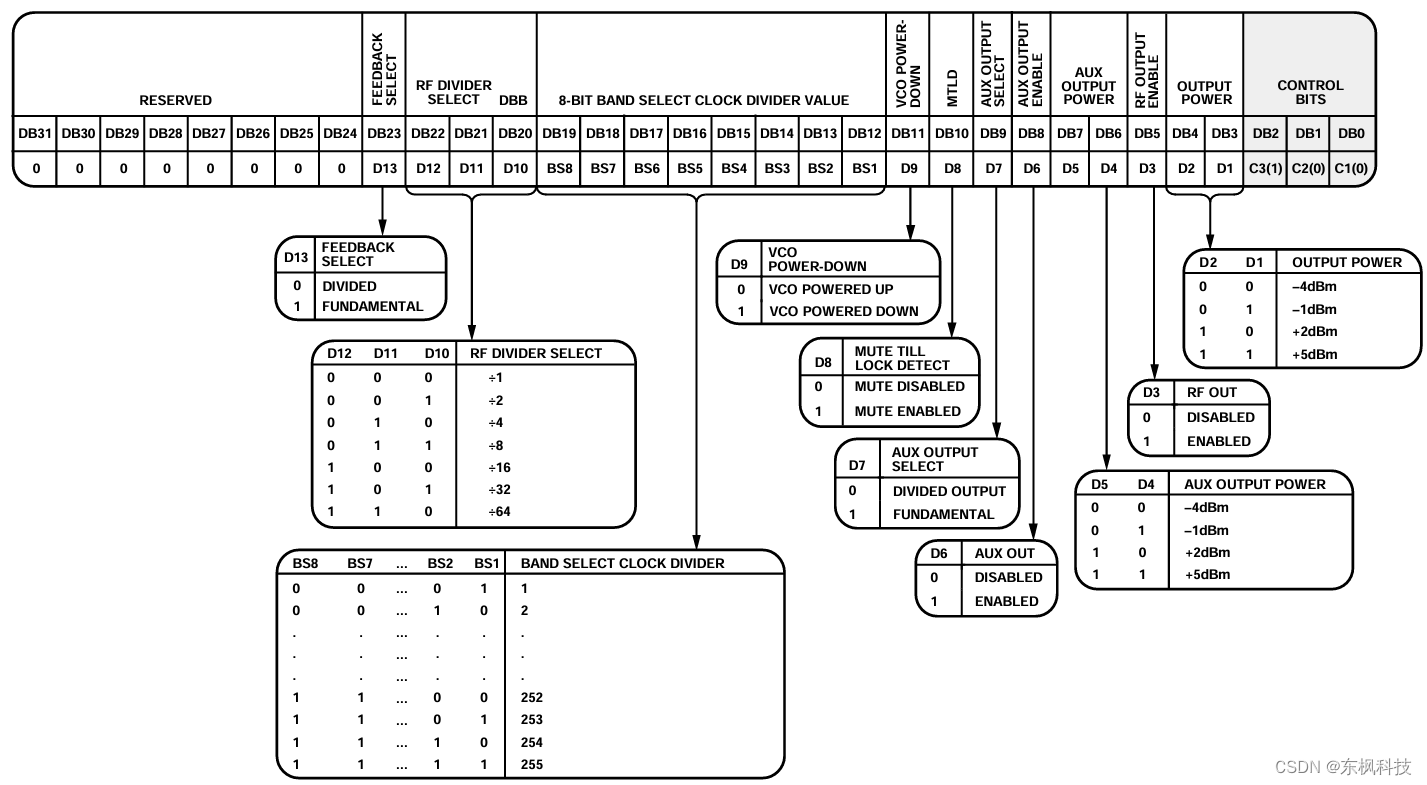

REGISTER 4

REGISTER 5

寄存器初始化序列

初始上电时,对电源引脚施加正确的电压后,ADF4351寄存器应按以下顺序启动:

- 寄存器5

- 寄存器4

- 寄存器3

- 寄存器2

- 寄存器1

- 寄存器0

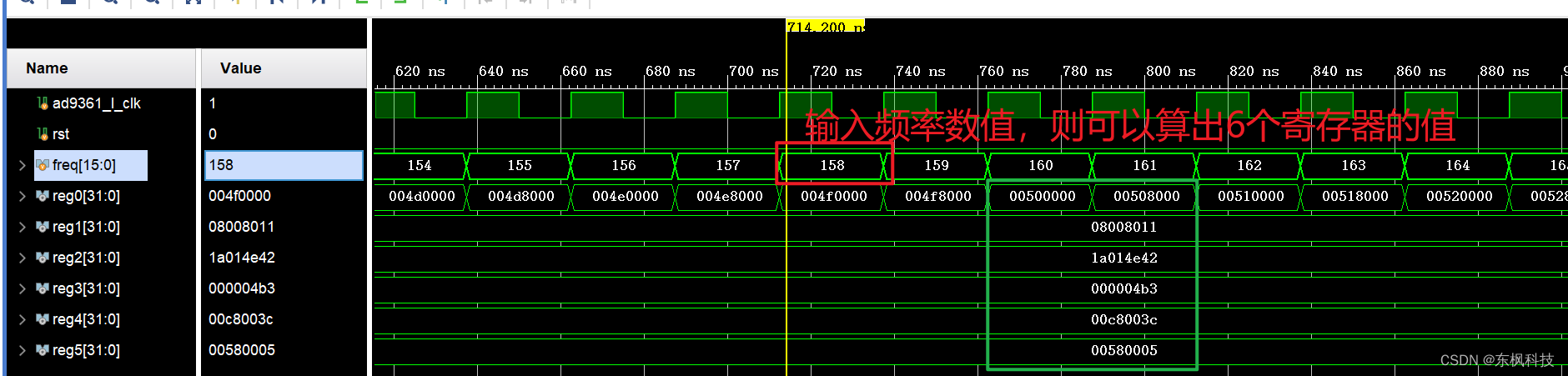

FPGA 根据频率计算寄存器数值

输入频率:4400M到35M

module adf4351_LUT_freq();

reg ad9361_l_clk,rst; initial beginad9361_l_clk=0;forever #12.5 ad9361_l_clk=~ad9361_l_clk;

end

initial beginrst=1;#25 rst=0;

endreg [15:0] freq;always @ (posedge ad9361_l_clk or posedge rst)

beginif(rst)beginfreq <= 16'd130;endelse if(freq < 16'd4400)beginfreq <= freq + 1'b1;endelse beginfreq <= freq;end

endwire [31:0] reg0,reg1,reg2,reg3,reg4,reg5;adf4351_reg_lut LUT(.clk_40(ad9361_l_clk),.rst(rst),.frequency(freq),.reg0(reg0),.reg1(reg1),.reg2(reg2),.reg3(reg3),.reg4(reg4),.reg5(reg5)

);

这篇关于【ADF4351】使用FPGA进行SPI寄存器配置、使用FPGA计算各个频率的频点,ADF4351配置程序的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!