本文主要是介绍【STA】SRAM / DDR SDRAM 接口时序约束学习记录,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1. SRAM接口

相比于DDR SDRAM,SRAM接口数据与控制信号共享同一时钟。在用户逻辑(这里记作DUA(Design Under Analysis))将数据写到SRAM中去的写周期中,数据和地址从DUA传送到SRAM中,并都在有效时钟沿处被锁存在SRAM中。在DUA从SRAM中取数据的读周期中,地址信号从DUA传送到SRAM中去,数据信号由SRAM输出给DUA。

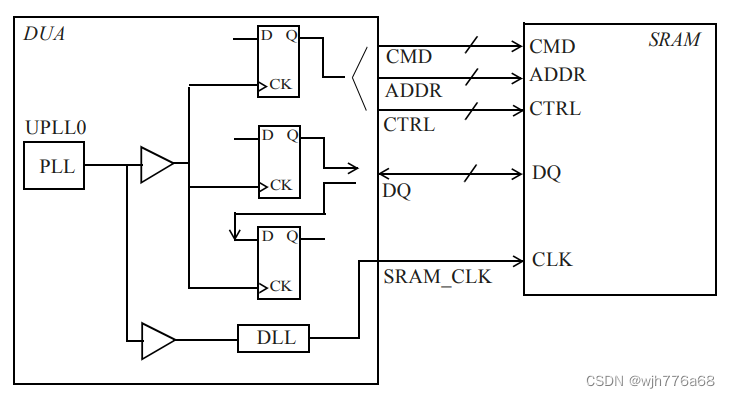

DUA与SRAM的接口简化如下

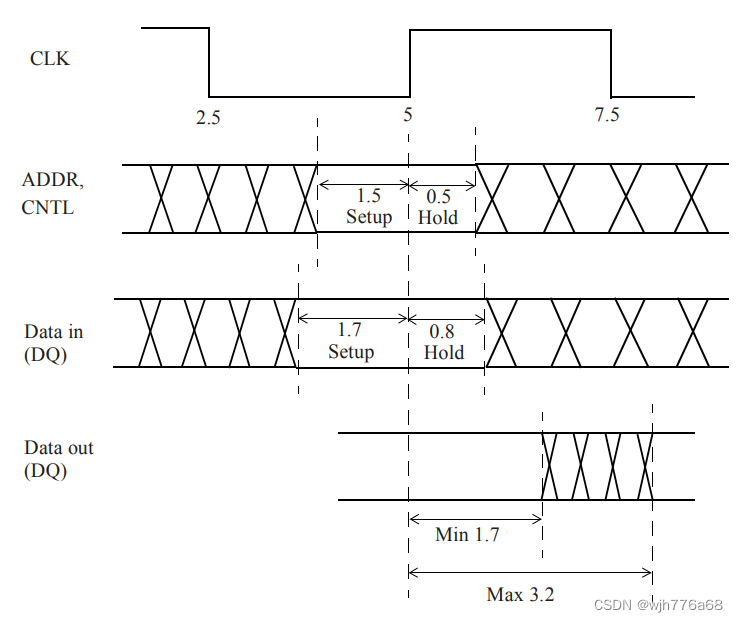

AC特性如下,图中Data in指写入SRAM,Data out指从SRAM读出

对应时序约束如下:

create_clock -name PLL_CLK -period 5 [get_pins UPLL0/CLKOUT]

create_generated_clock -name SRAM_CLK -source [get_pins UPLL0/CLKOUT] -divide_by 1 [get_ports

SRAM_CLK]

set_output_delay -max 1.5 -clock SRAM_CLK [get_ports ADDR[*]]

set_output_delay -min -0.5 -clock SRAM_CLK [get_ports ADDR[*]]

set_output_delay -max 1.7 -clock SRAM_CLK [get_ports DQ[*]]

set_output_delay -min -0.8 -clock SRAM_CLK [get_ports DQ[*]]

set_input_delay -max 3.2 -clock SRAM_CLK [get_ports DQ[*]]

set_input_delay -min 1.7 -clock SRAM_CLK [get_ports DQ[*]]

2. DDR SDRAM接口

相比SRAM,SDRAM的数据传输采用独立时钟(DQS),且采用双边沿触发的形式传输数据,数据位宽不限为1。在SDRAM的读模式期间,DQ与DQS均由SDRAM提供,DQ总线与数据选通引脚DQS双边沿对齐。在SDRAM的写模式期间,DQ与DQS均由DUA提供,DQS与DQ总线相移90度。为了降低偏斜平衡的实现复杂度,DQS与8个DQ(及一个dm_dbi_n)一组,在FPGA中能用SelectIO的一个半字节组对应。

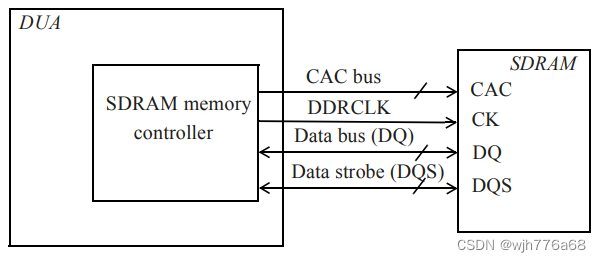

DUA与SDRAM的接口简化如下

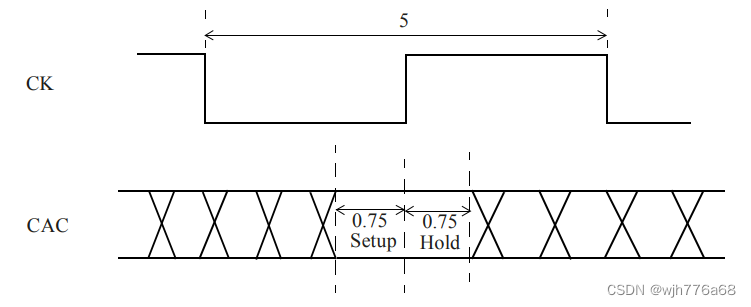

CAC控制引脚在DUA处的AC特性如下

对应时序约束如下:

create_generated_clock -name DDRCLK -source [get_pins UPLL0/CLKOUT] -divide_by 1 [get_ports

DDRCLK]

set_output_delay -max 0.75 -clock DDRCLK [get_ports CAC]

set_output_delay -min -0.75 -clock DDRCLK [get_ports CAC]

数据引脚在DUA处的AC特性需分情况考虑,

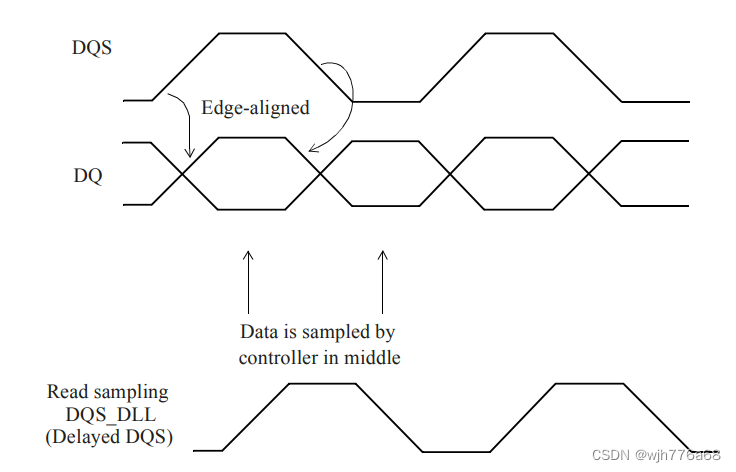

在读周期中,存储器输出的数据与DQS是边沿对齐的,为了满足DFF时序,通常使用DLL(或其它替代方法来实现四分之一周期延迟)来延迟DQS,从而使DQS的边沿对齐于数据有效窗口的中心。

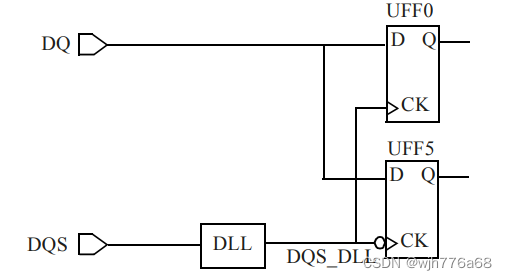

在DUA进行双边沿数据读取时,使用UFF0上升沿触发的触发器在DQS_DLL的上升沿捕获数据DQ,使用UFF5下降沿触发的触发器在DQS_DLL的下降沿捕获数据DQ。

对应的时序约束如下,对于下降沿的时序约束,使用-clock_fall标识

create_clock -period 5 -name DQS [get_ports DQS]

set_input_delay 0.4 -max -clock DQS [get_ports DQ]

set_input_delay -0.4 -min -clock DQS [get_ports DQ]

set_input_delay 0.35 -max -clock DQS -clock_fall [get_ports DQ]

set_input_delay -0.35 -min -clock DQS -clock_fall [get_ports DQ]

set_multicycle_path 0 -setup -to UFF0/D

set_multicycle_path 0 -setup -to UFF5/D

写周期中DQS边沿与从DUA内存储控制器输出的DQ信号相差四分之一周期,因此存储器可以直接使用DQS选通脉冲去捕获

数据。在存储器引脚处,DQS信号必须与DQ数据窗口的中心对齐。

对引脚处DQS与DQ的约束取决于DUA时钟的生成方式。

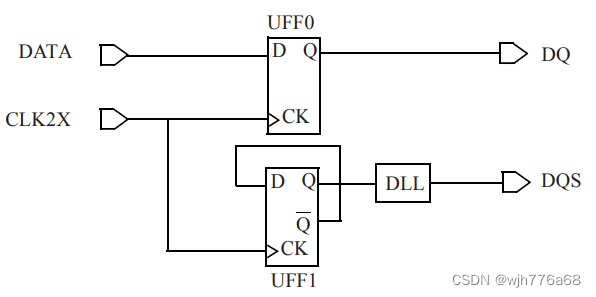

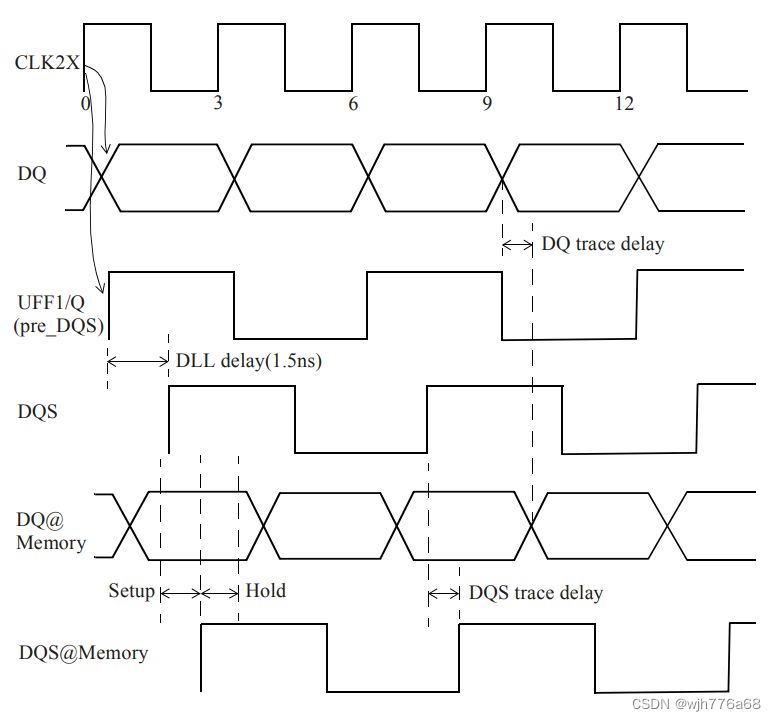

该方式下,对于DQ驱动采用两倍DQS频率的CLK2X时钟驱动,对应原理图如下

对应时序约束如下,DLL会对UFF1/Q进行延时,延时时长为1.5ns

create_clock -period 3 [get_ports CLK2X]

create_generated_clock -name pre_DQS -source CLK2X -divide_by 2 [get_pins UFF1/Q]

create_generated_clock -name DQS -source UFF1/Q -edges {1 2 3} -edge_shift {1.5 1.5 1.5} [get_ports DQS]

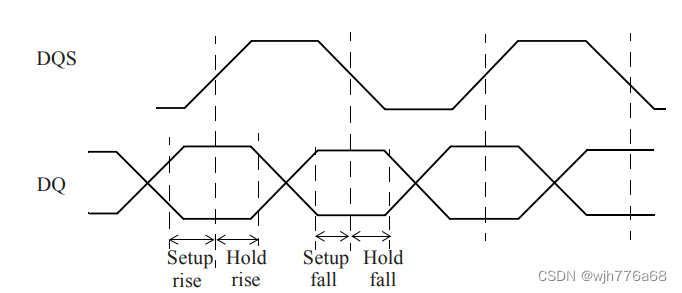

假设DDR SDRAM的DQ和DQS引脚之间建立时间要求分别为DQ上升沿的0.25ns和下降沿的0.4ns。类似地,假设DQ引脚上升

沿和下降沿的保持时间要求分别为0.15ns和0.2ns。DQS输出上的DLL延迟已设置为四分之一周期,即1.5ns,波形如下

时序约束如下,利用-rise、-fall区分上升与下降沿

set_output_delay -clock DQS -max 0.25 -rise [get_ports DQ]

set_output_delay -clock DQS -max 0.4 -fall [get_ports DQ]

set_output_delay -clock DQS -min -0.15 -rise [get_ports DQ]

set_output_delay -clock DQS -min -0.2 -fall [get_ports DQ]

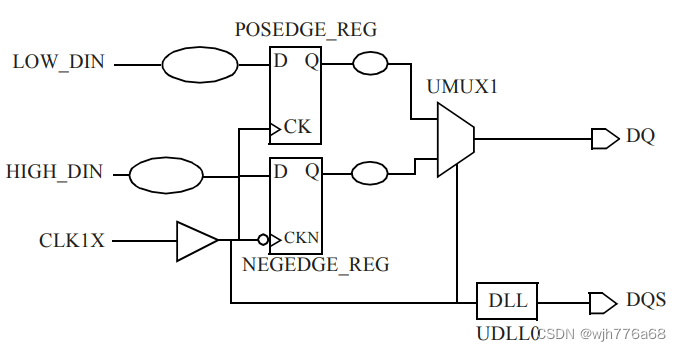

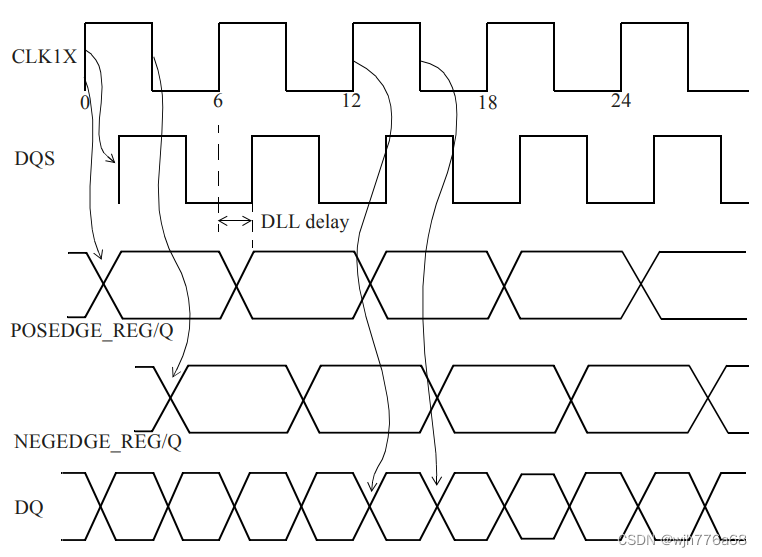

使用POSEDGE_REG DFF与NEGEDGE_REG DFF分别在CLK1X上升沿、下降沿生成DQ数据,利用CLK1X的高低电平作为选择器的选择信号,CLK1X为高电平时,触发器NEGEDGE_REG的输出发送到DQ;而当CLK1X为低电平时,触发器POSEDGE_REG的输出发送到DQ。从而保证在时钟CLK1X的两个边沿都有新的数据输出DQ。

每个触发器都需要有半个CLK1X周期将数据传播到多路复用器的输入端,以保证在由CLK1X边沿选择输入数据之前,已在多路复用器的输入端口上准备好了输入数据。

对应波形如下:

对应时序约束如下:

create_clock -name CLK1X -period 6 [get_ports CLK1X]

create_generated_clock -name DQS -source CLK1X -edges {1 2 3} -edge_shift {1.5 1.5 1.5} [get_ports DQS]

set_output_delay -max 0.25 -clock DQS [get_ports DQ]

set_output_delay -max 0.3 -clock DQS -clock_fall [get_ports DQ]

set_output_delay -min -0.2 -clock DQS [get_ports DQ]

set_output_delay -min -0.27 -clock DQS -clock_fall [get_ports DQ]

为了减少由于DRAM和DUA处的阻抗不匹配而引起的反射,DDR接口的DQ和DQS信号在读模式和写模式下可能使用终端电阻ODT(On-Die Termination)。在使用ODT的情况下,STA将无法提供足够的精度。这时需要使用如详尽的电路级仿真的方式来验证SDRAM的接口时序。

3. DAC接口

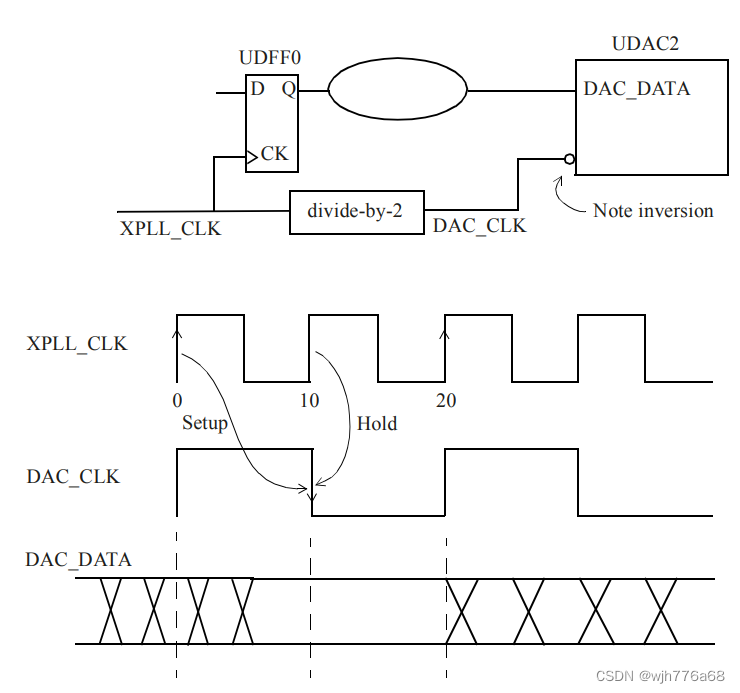

下图展示了一个视频DAC(数模转换)转换接口,高速时钟将数据传输到DAC的低速时钟接口,其中UDFF0采用上升沿触发,UDAC2采用下降沿触发

在这种情况下,可以根据需要将从快时钟域到慢时钟域的接口指定为多周期(两周期)路径,也可以将建立时间视作单周期

(XPLL_CLK)路径。最关键的保持时间检查是在发起沿和捕获沿重合处执行的。

这篇关于【STA】SRAM / DDR SDRAM 接口时序约束学习记录的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!