本文主要是介绍【LabVIEW FPGA】CIC滤波器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、CIC滤波器应用概述

在通信数字信号上下变频时,经常会用到对数字信号的升采样和降采样,即通过CIC数字速率器实现变采样率。

二、滤波器IP

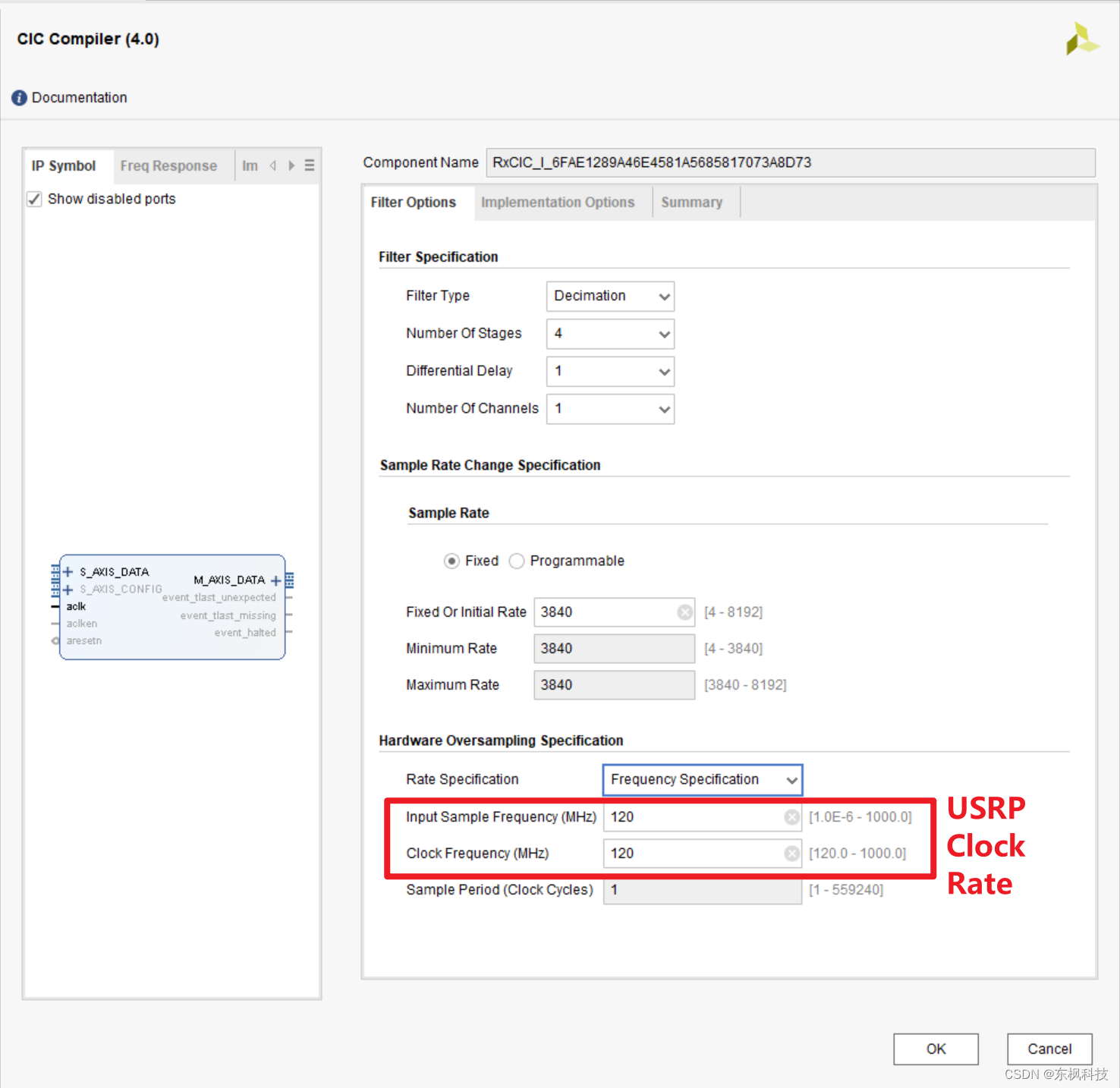

首先设置滤波器基本参数(filter specification)

- 滤波器类型(Filter Type):设置CIC滤波器模式为抽取Decimation或插值Interpolation;

- 级联数目(Number Of Stages):设置级联的CIC滤波器级数;

- 差分延时(Differential Delay):设置差分延时,IP核只能设置为1或者2;

- 通道数(Numebr Of Channels):设置多通道滤波器。

sample rate change specification

- 采样速率设置(sample rate)

这里可以选择可程序配置和固定参数类型,其中抽取或者插入系数就对应R值,这里设置为6,即6倍抽取。

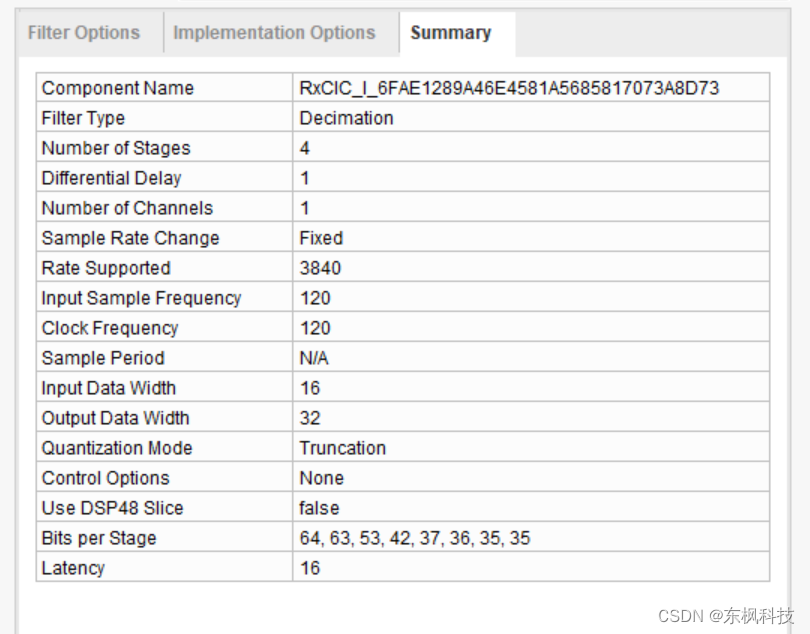

120,000,000 / 3840 = 31,250

硬件采样处理规范(hardware oversampling specification)

选项卡主要是配置输入数据速率,CIC处理速率。

- 输入采样率(input sample frequncy)就是输入信号的采样频率。

- 时钟频率(clock frequncy )就是进行运算时的频率。

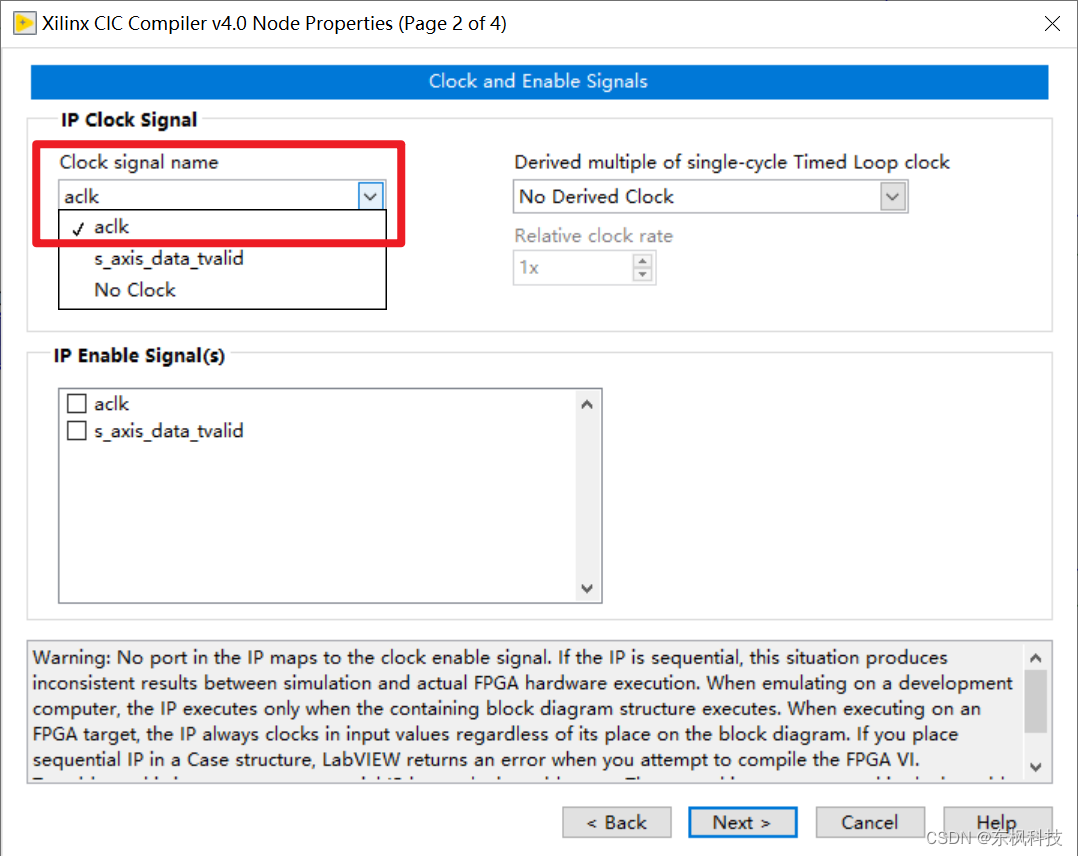

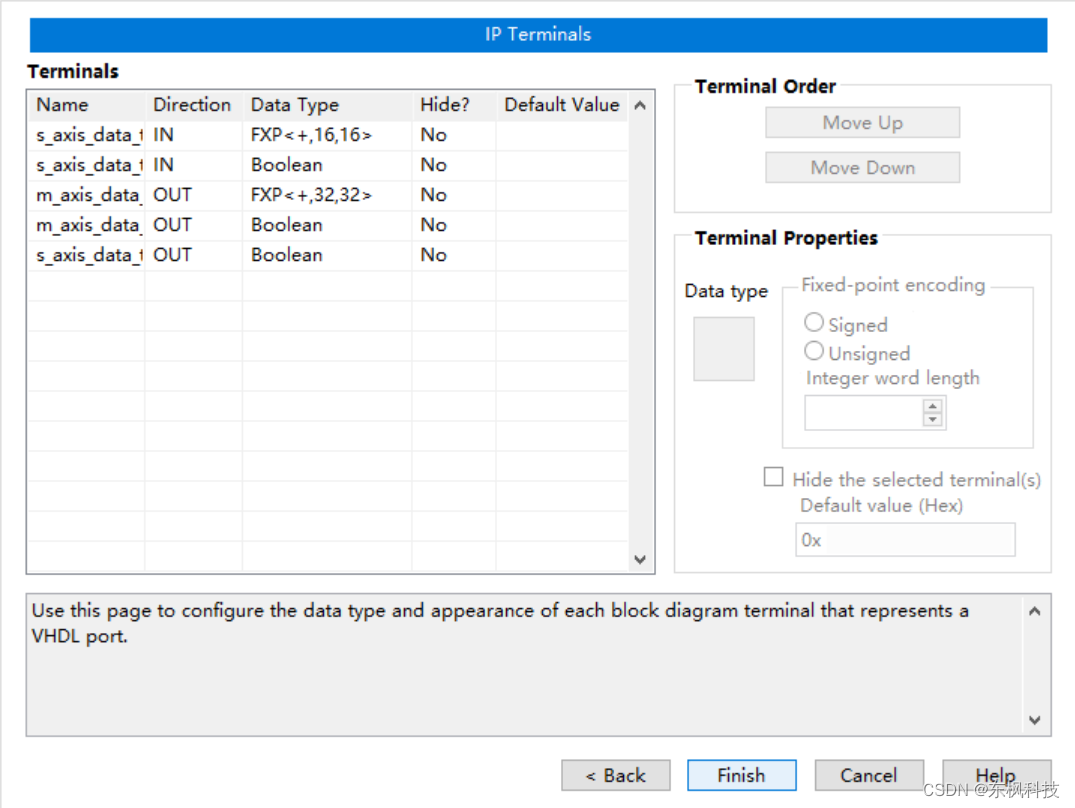

labview

这篇关于【LabVIEW FPGA】CIC滤波器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!