本文主要是介绍基于FPGA的ECG信号滤波与心率计算verilog实现,包含testbench,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

1.算法运行效果图预览

2.算法运行软件版本

3.部分核心程序

4.算法理论概述

4.1 ECG信号的特点与噪声

4.2 FPGA在ECG信号处理中的应用

4.3 ECG信号滤波原理

4.4 心率计算原理

4.5 FPGA在ECG信号处理中的优势

5.算法完整程序工程

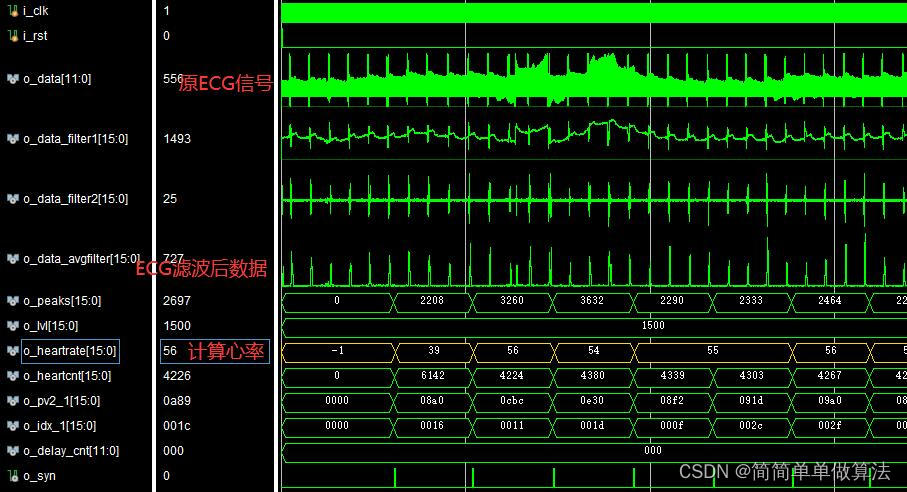

1.算法运行效果图预览

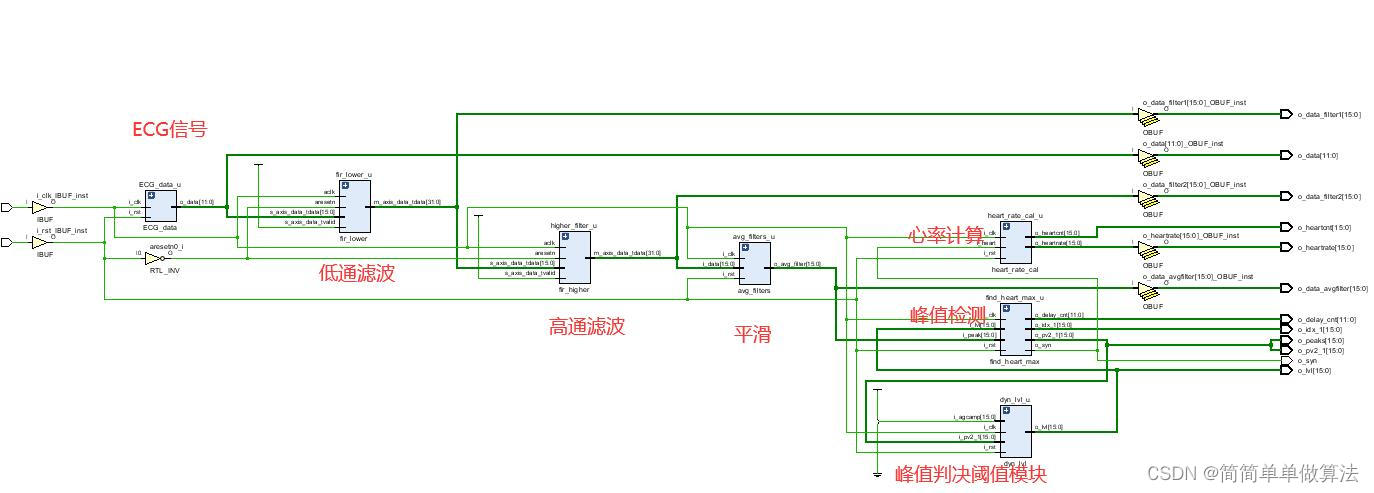

其RTL结构如下:

2.算法运行软件版本

vivado2019.2

3.部分核心程序

...................................................................//调用心率数据

ECG_data ECG_data_u(.i_clk (i_clk), .i_rst (i_rst), .o_data(o_data));//low filter

wire signed[31:0]w_channel_output1;fir_lower fir_lower_u(.aresetn (~i_rst), // input sclr.aclk (i_clk), // input clk.s_axis_data_tvalid (1'b1), // output rfd.s_axis_data_tready (),.s_axis_data_tdata ({o_data[11],o_data[11],o_data[11],o_data[11],o_data}), .m_axis_data_tvalid (), .m_axis_data_tdata(w_channel_output1) // output [24 : 0] dout

);

assign o_data_filter1=w_channel_output1[25:10];//high filter//这里和论文不一样,我再增加一个高频滤波

wire signed[31:0]w_channel_output2;

fir_higher higher_filter_u(.aresetn (~i_rst), // input sclr.aclk (i_clk), // input clk.s_axis_data_tvalid (1'b1), // output rfd.s_axis_data_tready (),.s_axis_data_tdata ({o_data_filter1}), .m_axis_data_tvalid (), .m_axis_data_tdata(w_channel_output2) // output [24 : 0] dout

);assign o_data_filter2=w_channel_output2[25:10];//平均滤波

avg_filters avg_filters_u(.i_clk (i_clk), .i_rst (i_rst), .i_data (o_data_filter2), .o_avg_filter(o_data_avgfilter));//===============================================================

wire[15:0]o_pv2_1;dyn_lvl dyn_lvl_u(.i_clk (i_clk), .i_rst (i_rst), .i_agcamp(16'd1500), .i_pv2_1 (o_pv2_1), .o_lvl (o_lvl));find_heart_max find_heart_max_u(.i_clk (i_clk), .i_rst (i_rst), .i_lvl (o_lvl), .i_peak (o_data_avgfilter), .o_pv2_1 (o_pv2_1), .o_idx_1 (o_idx_1), .o_delay_cnt(o_delay_cnt), .o_syn (o_syn), .curr_state (), .cnten (), .cnt0 (), .cnt1 (), .cnt2 (), .cnt3 (), .cnt4 (), .max_1 (), .max_2 (), .max_3 (), .max_4 ());assign o_peaks = o_pv2_1;//计算心率

heart_rate_cal heart_rate_cal_u(.i_clk(i_clk), .i_rst(i_rst), .i_heart (o_syn), .o_heartrate(o_heartrate), .o_heartcnt (o_heartcnt));endmodule

37_006m4.算法理论概述

心电图(ECG)是医学领域中常用的一种无创检测技术,用于记录和分析心脏的电活动。由于ECG信号微弱且易受到噪声干扰,因此在采集和处理过程中需要进行滤波以提取有效信息。同时,根据滤波后的ECG信号,可以进一步计算心率等生理参数。现场可编程门阵列(FPGA)以其并行处理能力和可重构性,在ECG信号处理中发挥着重要作用。

4.1 ECG信号的特点与噪声

ECG信号是一种低频、微弱的生物电信号,其频率范围主要集中在0.05Hz至100Hz之间。典型的ECG波形包括P波、QRS波群和T波等。在信号采集过程中,ECG信号容易受到基线漂移、工频干扰、肌电干扰和电极接触噪声等的影响。

4.2 FPGA在ECG信号处理中的应用

FPGA作为一种高性能的数字信号处理器件,可以实现复杂的数字滤波算法,以去除ECG信号中的噪声干扰。常用的数字滤波器包括低通滤波器、高通滤波器和带通滤波器等。

4.3 ECG信号滤波原理

- 低通滤波器:用于去除高频噪声,如肌电干扰和工频干扰。其数学表达式为:

(H(z) = \sum_{k=0}^{N} b_k z^{-k} / \sum_{k=0}^{M} a_k z^{-k})

其中,(H(z))为滤波器的传递函数,(b_k)和(a_k)为滤波器的系数,(N)和(M)为滤波器的阶数。

-

高通滤波器:用于去除基线漂移等低频噪声。其数学表达式与低通滤波器类似,但系数不同。

-

带通滤波器:结合低通和高通滤波器的特点,仅允许特定频率范围内的信号通过,以提取ECG信号中的有效信息。

4.4 心率计算原理

心率计算通常基于ECG信号中的R波进行检测。R波是ECG信号中幅度最大、最易于识别的波形之一。通过检测R波的间隔时间(RR间期),可以计算出心率。

心率(HR)的计算公式为:

(HR = 60 / RR)

其中,RR为两个相邻R波的时间间隔(以秒为单位)。

在FPGA中实现心率计算时,通常需要先对滤波后的ECG信号进行阈值检测或峰值检测,以准确识别R波的位置。然后,通过计时器或计数器测量RR间期,并根据上述公式计算心率。

4.5 FPGA在ECG信号处理中的优势

-

并行处理能力:FPGA可以同时处理多个数据通道,实现高速的ECG信号采集和处理。

-

可重构性:FPGA可以根据不同的应用需求灵活配置滤波器和心率计算算法。

-

低功耗:相比其他高性能处理器,FPGA在功耗方面具有优势,适用于便携式医疗设备。

5.算法完整程序工程

OOOOO

OOO

O

这篇关于基于FPGA的ECG信号滤波与心率计算verilog实现,包含testbench的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!