本文主要是介绍工具与大脑完美结合,才能写出世上最棒的Verilog代码,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

工具与大脑完美结合,才能写出世上最棒的Verilog代码

EDA工具的利与弊

很多新生代的FPGA工程师都没使用过使用原理图输入进行FPGA设计,没有经历过那些“画原理图和连线”的工作,这得益于HDL(Hardware Description Language) 硬件描述语言和语言综合工具及其它EDA相关工具的推广,使广大的工程师的工作重心从底层连线上转移到功能实现上。

从这方面讲EDA工具极大地提高了工作效率,而且随着这些工具的发展整个FPGA设计越来越方便,尤其一些高级语言的引入让整个FPGA开发效率越发提高,但是还是需要警惕EDA工具的“弊端”。

现在越来越多的FPGA工程师基本只关心功能的实现,而基本不关心自己的电路实现形式,都是以功能为目标,后期的优化交给工具就OK了。

这种思想的的后果就是在用HDL描述电路时(大部分以为自己写的是程序),脑袋里没有或者非常模糊的电路概念,对于代码后期的综合成什么样子和映射(route)到FPGA芯片后是什么样子完全没想法,这样做的后果就是完全没有充分利用FPGA的特点和结构,一旦遇到工具不能解决的问题,自己就束手无策,这就是过份依赖工具的后果。

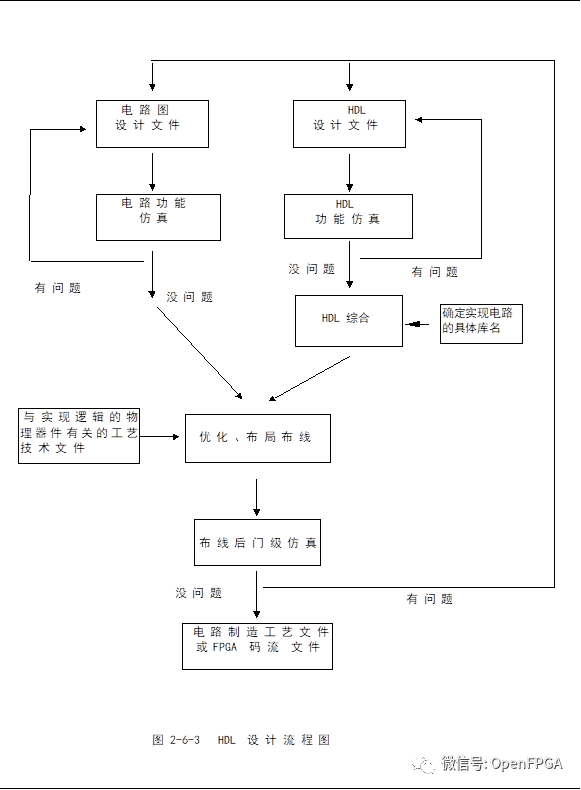

HDL和FPGA是怎么“牵手”的

HDL转换成FPGA可以运行的“程序”得益于两个过程:Synthesis 和 Optimization。Synthesis是把行为级描述通过算法转换为门级的描述,这个过程是与约束没有关系的;Optimization的作用则是把上一步的门级描述在用户的约束作用下(约束的重要性)通过算法映射到FPGA的单元结构上。

整个过程如下图所示:

所以我们发现HDL的设计是会间接影响到最后的结果的,也就是我们的Code Style不一样Synthesis部分就已经大部分决定了最后的设计的性能。简单举个例子:

16选1选择器:

当我们使用case这一算法级描述的时候,综合结果如下:

当我们使用内部BUFT进行描述时(BUFT可以参考:http://blog.sina.com.cn/s/blog_ea3189e20102wzhl.html),综合结果如下:

也就是说,我们不同的Code Style,最后的综合、实现结果也是不一样的。

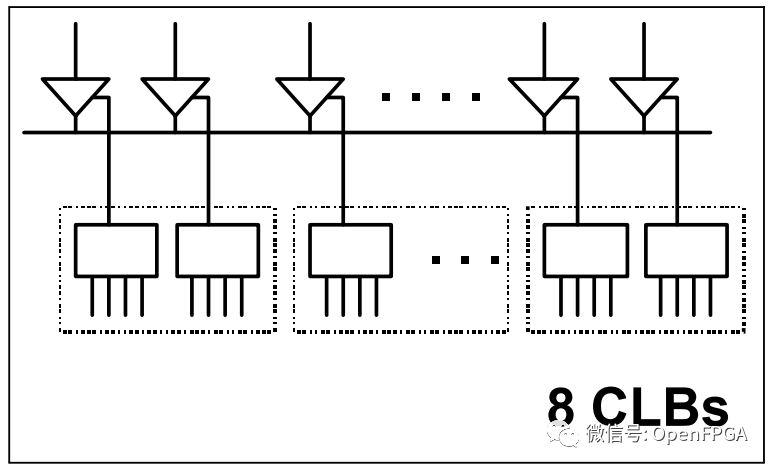

最后我们也知道现在大部分FPGA由查找表(LUT)、时序单元和一些先进结构组成(进位链等),由于最小单元固定,所以基本单元的延时是固定的,我们在设计代码时需要充分考虑使用了多少级查找表或者进位链,这样我们可以尽可能的减少延时,所以在设计时我们就需要考虑好如何根据FPGA的器件特点更好的利用FPGA资源。

关于FPGA的器件特点推荐《简谈 Xilinx FPGA 原理及结构》和《FPGA原理和结构PDF》。

进行大型逻辑设计时,布局规划也是我们需要考虑的问题,这里就不展开赘述了,可以查看《FPGA 的布局规划艺术》。

总结

上面说了这么多,无非就是想让大家明白:不要过分依赖工具,如果把整个FPGA设计看做是化学变化的话,那么我们使用的工具只是起到催化剂的作用,我们自己的知识、设计技巧及Code Style才是参加这一化学变化的反应分子,才是最重要的因素(突然想到2H2O——2H2↑+O2↑,难受!)。所以我们需要将自己写作的Code Style和工具、FPGA特点结合起来,这样才能写出最棒的代码。

这里说几个常用的Code Style:

1、减少扇出-高扇出会造成布线延时变长;2、复位方案-复位的选择对性能是有影响的,根据厂家的推荐选择合适的复位方式;3、使用专用布局布线资源-可以根据需求选择专用的低延时布线资源;。。。上面只是简单说了几个,这里推荐华为的Code Style文档《华为经典FPGA设计全套入门技巧资料分享》作为参考,后续可以根据自己的习惯和经验进行修改。

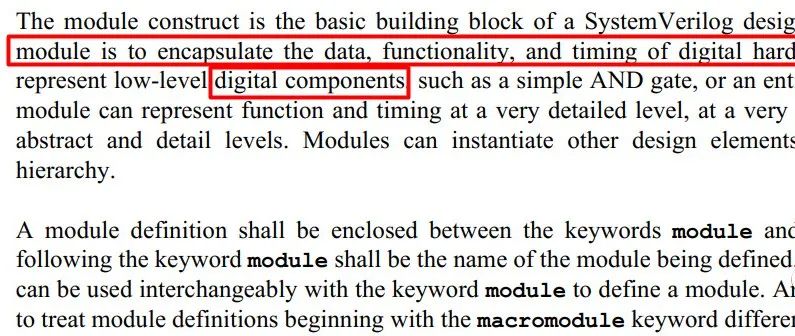

你真的理解Verilog 中的module吗?

优秀的 Verilog/FPGA开源项目介绍(十一)- SPI/SPI FLASH/SD卡

Zynq MPSOC 电子书免费下载

基于FPGA的数字识别-实时视频处理的定点卷积神经网络实现

这篇关于工具与大脑完美结合,才能写出世上最棒的Verilog代码的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!