本文主要是介绍FPGA时序分析与时序约束(五)——使用Timing Analyzer进行时序分析与约束,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Quartus的安装路径下会自带有例程,通过fir_filter进行学习如何使用Timing Analyzer进行时序分析与约束。

1.1 创建时序网表

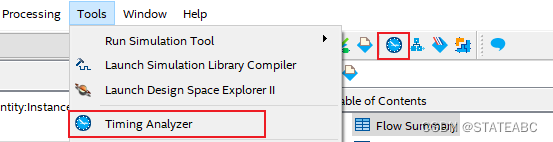

打开fir_filter并进行综合后可通过菜单栏Tool->Timing Analyzer或工具栏按钮运行Timing Analyzer。

根据前面提到的,时序分析工具需要网表来执行时序分析,因此先创建Post-Map时序网表。在菜单栏Netlist->Create Timing Netlist,选择Post-Map会自动生成Tcl命令。

1.2 时钟约束

时序约束可以分为四个主要步骤,即时钟约束(Create Clock)、输入/输出接口约束(Input/Ouput Delays,I/O约束)、时钟分组和跨时钟约束(Clock Groups and CDC)、时序例外约束(Timing Exceptions)。

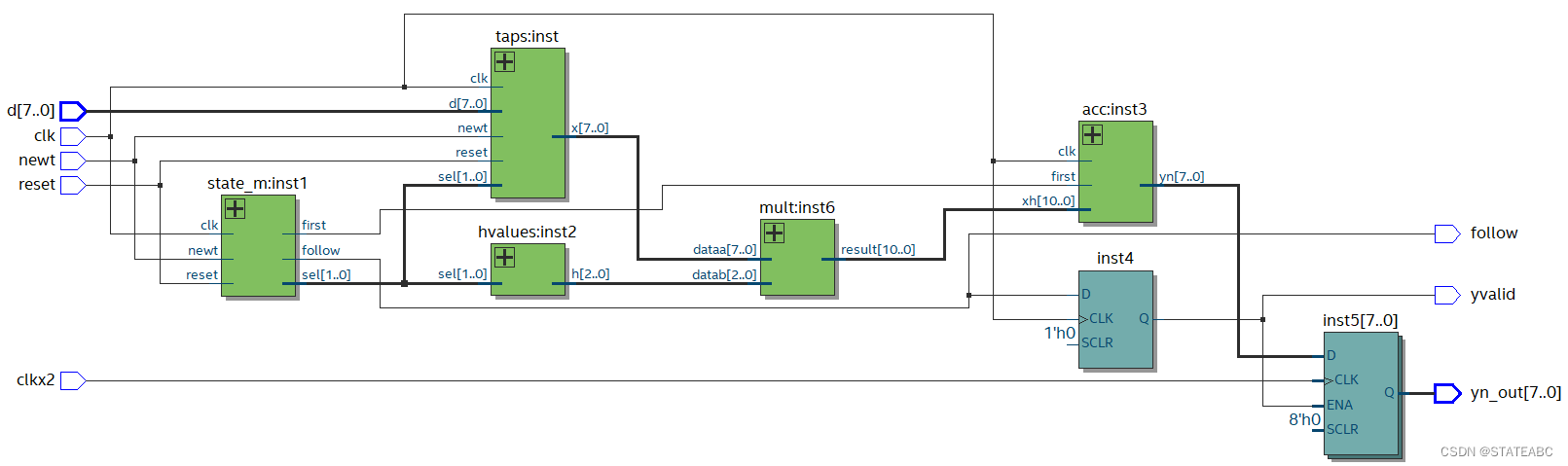

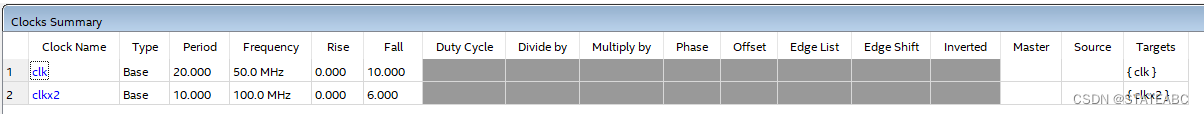

因此对工程进行时钟约束,通过RTL图可以看出有两个时钟,clk是50%占空比的50MHz时钟,clkx2是60%占空比的100MHz时钟。

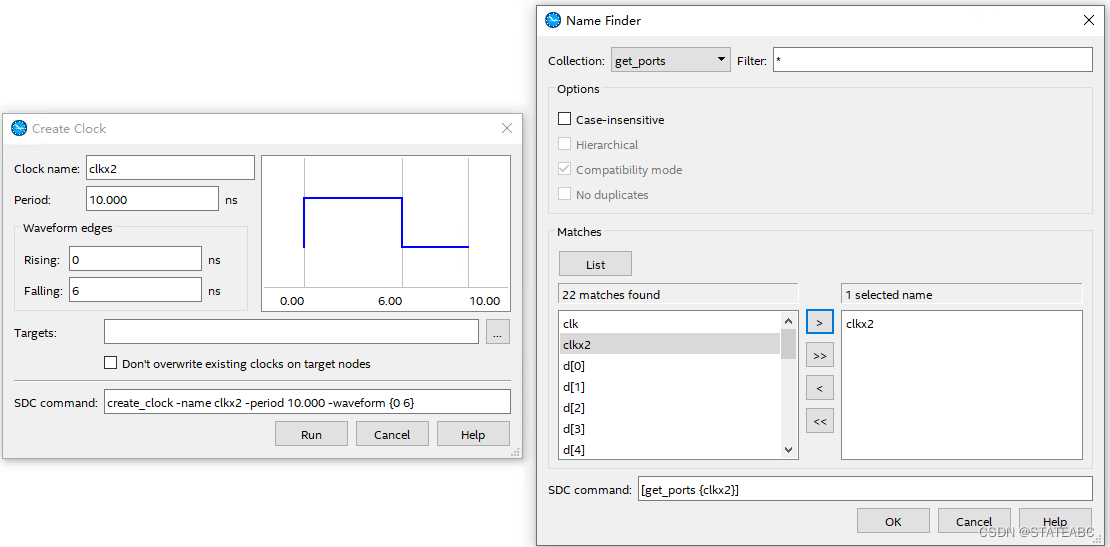

在菜单栏Constraints->Create Clock,出现Create Clock对话框。在该对话框中设置时钟名称、时钟周期以及上升沿和下降沿的时刻,然后在Target栏选择对应的端口。当进行设置时,SDC ommand也会随之列出等效的SDC约束命令,也可以通过输入该命令来创建时钟约束。默认情况下,如果未使用 -Waveform egdes选项,那么create clock命令就会默认 50/50 的占空比。

clk为50MHz时钟,时钟周期为1/50MHz=20ns。

clkx2为100MHz时钟,时钟周期为1/100MHz=10ns,60%占空比则上升沿在0ns、下降沿在6ns。

创建时序约束后,需要在菜单栏Netlist->Update Timing Netlist对时序网表进行更新(task工具栏也可以),将所有时序要求应用到时序网表。只要应用了新的时序约束,就必须对时序网表进行更新。

在为设计指定时钟约束并更新时序网表后,需要创建SDC文件并将上面的约束保存到SDC文件中,约束不会自动保存,因此在菜单栏Constraints->Write SDC File,在Write SDC File对话框输入文件名称并保存。

最后生成SDC约束报告(SDC Assignments Report),SDC约束报告了在指定设计中包含的所有时序约束,在菜单栏Report->Diagnostic->Report SDC;然后生成时钟总结报告( Clocks Summary Report),总结设计中所有的时钟,在菜单栏Report->Diagnostic->Report Clocks。

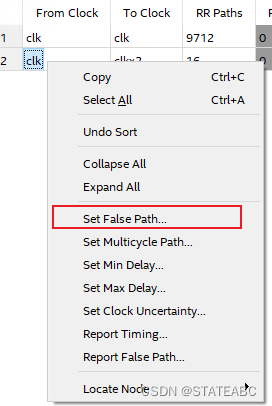

生成时钟传输报告 (Clock Transfers Report),使用Report Clock Transfers命令生成一个报告来验证所有的时钟到时钟传输都是有效的。这种报告包含设计中所有的时钟到时钟传输。在菜单栏Report->Diagnostic->Report Clock Transfers。Clock Transfers报告表明在clk (源时钟) 和clkx2(目的时钟) 之间存在跨时钟域路径,共有16条路径,其中clk为源节点提供时钟,clkx2为目的节点提供时钟。

1.3 伪路径约束

在 fir filter 设计中,不必分析clk至clkx2的时钟传输,因为它们是忽略路径。通过以下方式声明 clk 至 clkx2 的路径为伪路径:

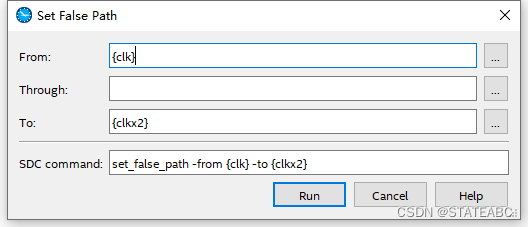

1.在 Clock Transfers 报告中,在 From Clock 列选择clk,右击并选择“Set FalsePaths”这个命令表明将所有由 clk 驱动的源寄存器到由 clkx2 驱动的目的寄存器之间的路径设为伪路径。

2.使用set_clock groups声明两个时钟域之间的路径为伪路径。例如,set clock groups -asynchronous -group [get clocks clk] -group [get clocks clkx2]该命令表明clk到clkx2以及clkx2到 clk的所有路径为伪路径。

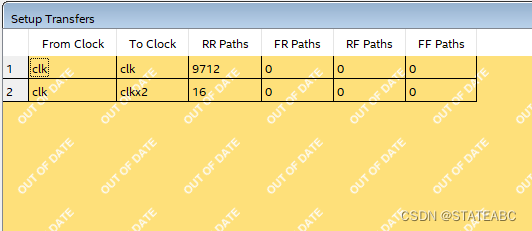

当完成该程序后,TimeQuest Timing Analyzer变成黄色(Out of Date)表明当前Clock Transfers报告是过时的,表明报告面板不包含反映Timing Analyzer中当前状态的约束的结果。

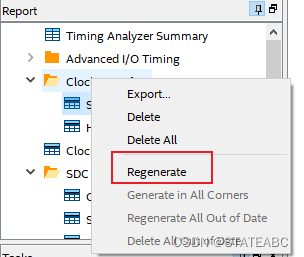

而添加新的时序约束(设置伪路径),也需要UpdateTiming Netlist更新时序网表。然后更新报告面板,右击报告面板列表中任何过时(out-of-date)的报告,并选择 Regenerate all。

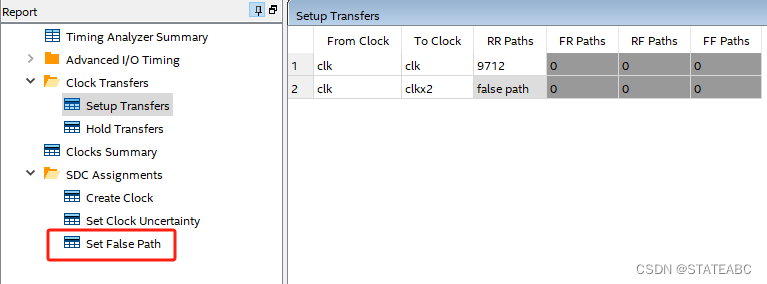

重新生成报告后,可以看到在SDC Assignments报告栏多了一个“Set False Path”约束。同时打开 Clock Transfers 报告可以看到由clk到clkx2的路径被声明为伪路径,意味着时序分析工具将不再分析这些路径(例外约束)。

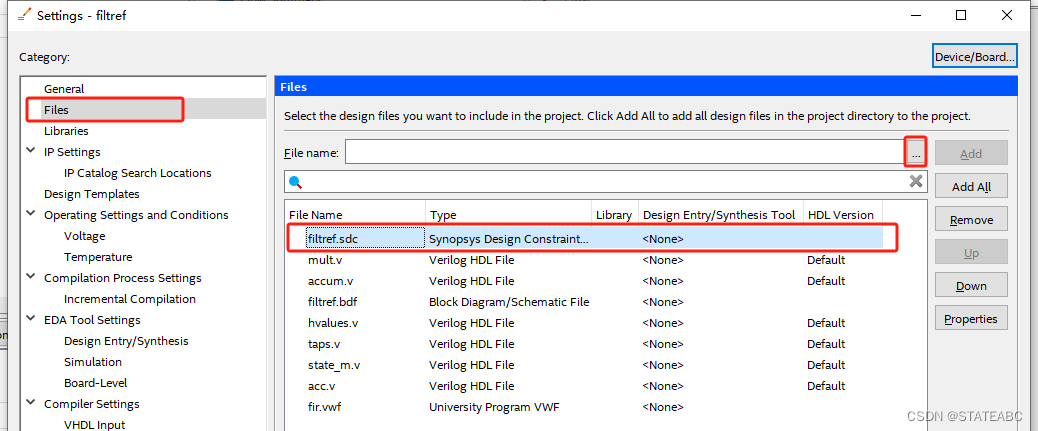

在指定设计中所有的时钟约束和伪路径后,通过Write SDC File将时序约束和例外保存到 SDC 文件,然后将SDC文件添加到工程中。在Quartus->Assignments->Settings->Files->...,找到保存的sdc文件并添加。

工程全编译后就能看到Timing Analyzer生成的报告。

1.4 输入输出约束

编译完成后,运行 TimeQuest Timing Analyzer,Create Timing Netlist、 Read SDC和 Update Timing Netlist命令依次在Tasks面板中执行,自动生成时序网表,读取 SDC 文件并更新时序网表。

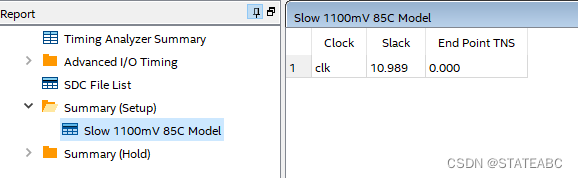

点击Report Setup Summary生成建立总结报告 (Summary Setup),对设计中的所有时钟进行检查,来验证没有出现违规。时钟建立检查确保每个寄存器至寄存器的传输不违反 SDC 指定的时序约束。 clkx2时钟没有出现在 Summary(Setup)报告中,因为clk 和 clkx2之间所有的时钟路径已经声明是伪路径。此外,fir filter设计不包含任何由 clkx2 来驱动的寄存器到寄存器的路径。 Summary(Setup) 报告中的Slack列表明clk能满足约束,并有10.989ns的余量。End Point TNS列是指定时钟域中所有的总负裕量 (TNS,Total Negative Slack) 的总和。使用这个值来测量指定时钟域中失败路径的总数。

点击 Report Hold Summary,在设计中生成一个时钟保持检查总结。Summary (Hold) 报告表明 clk 时钟节点符合时序约束,并有0.326ns的余量。

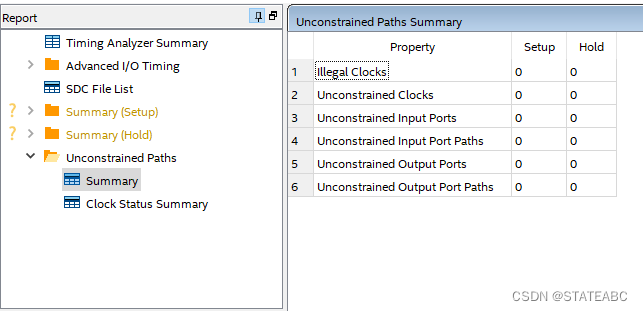

在执行全编译之前,指定所有的时序约束和例外,这样可以确保Fitter优化设计中的关键路径,使用Report Unconstrained Paths命令验证已经约束fir filter设计中的所有路径。 如下图所示,Unconstrained Paths 总结报告表明有大量的未约束路径,并详细介绍了这些路径的类型。要充分约束此设计,需要利用由Timing Analyzer所提供的整套SDC约束。

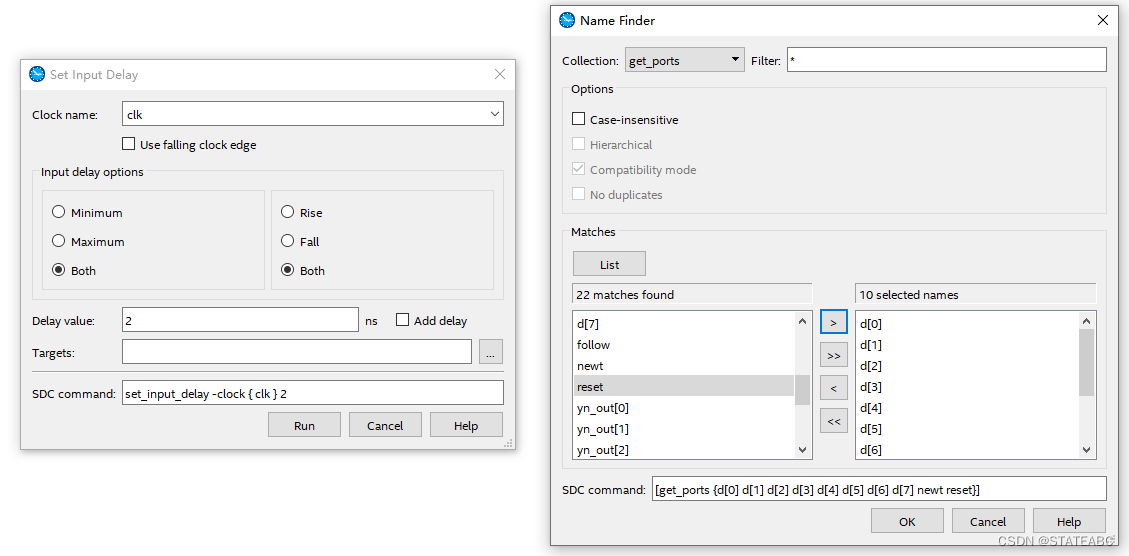

总结报告中的未约束路径集中在Input/0utput Ports上,因此可以使用Set Input Delay和Set Output Delay需要约束所有的输入和输出端口。

在菜单栏Constraints->Set Input Delay

在菜单栏Constraints->Set Output Delay

通过Write SDC File将输入输出延迟约束保存到 SDC 文件中,更新时序网表,重新生成Unconstrained Paths Summary,验证所有设计中的端口都已经加上了约束。

Timimg Analyzer还可以对设计的时钟或节点生成特定的时序检查报告。在Tasks面板中,双击 Report Timing,出现Report Timing对话框。

对话框设置完成后点击“Report Timing”,会生成一个报告。报告会列出10条最差路径,这些路径均由clk驱动目的寄存器,并且目的寄存器为 acc:inst3 result。

在“Summary of Paths”一栏列出了这些路径的起点和终点,以及启动时钟和锁存时钟等信息,其中第一列“Slack”指示了这些路径是否满足时序要求,以及满足或违反时序要求的程度。当Slack 为正时,表示满足时序要求:Slack为负时表明该路径不满足时序要求,那么就需要针对该路径进行修复。

点击 Summary of Paths 中的任意一个时序路径可以在下方看到它的详细信息,比如在“Data Path”中列出了该路径中信号到达各个节点的延迟信息。时序分析工具通过比较数据到达时间(Data Arrival Times) 和数据要求时间 (Data Require Times) 来验证电路性能并检测可能出现的时序违规。“Waveform”一列给出了时序路径的波形图,从图中可以更直观

的比较各个时序参数。

Report Timing 默认分析的是建立时间,同样可以选择分析其他类型(Analysis Type),比如保持时间、恢复/移除时间等。

参考文献:

正点原子FPGA静态时序分析与时序约束_V2.3

Intel Quartus Prime Standard Edition 用户指南: Timing Analyzer

这篇关于FPGA时序分析与时序约束(五)——使用Timing Analyzer进行时序分析与约束的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!