本文主要是介绍SATA驱动中FIS命令处理(详细)流程附代码和协议解析,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

- 一、简介

- 二、命令处理详细流程

- 2.1 总体过程总结

- 2.2 内存布局

- 2.2.1 具体内存分配规则

- 2.2.2 具体命令填充

- 2.2.3 命令触发流程

- 2.2.4 其他注意事项

- 三、其他相关链接

- 1、SATA模块之HBA卡开发总结(一)

- 2、SATA信息传输FIS结构总结

- 3、PCIe物理层总结-PCIE专题知识(一)

- 4、PCIe数据链路层图文总结-PCIe专题知识(二)

- 5、SSD硬盘SATA接口和M.2接口区别总结

一、简介

本文主要讲述在SATA模块命令的处理、数据的传输和内存分布详细过程,同时讲述如何通过FIS用于Host和device之间信息传输。

二、命令处理详细流程

2.1 总体过程总结

1、构造FIS命令;

2、填充Command Table;

3、填充Command Header;

4、通知Host或Device处理命令;

2.2 内存布局

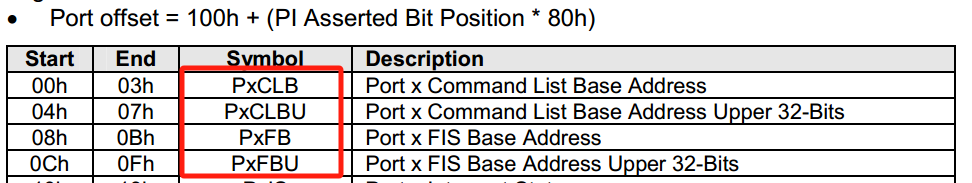

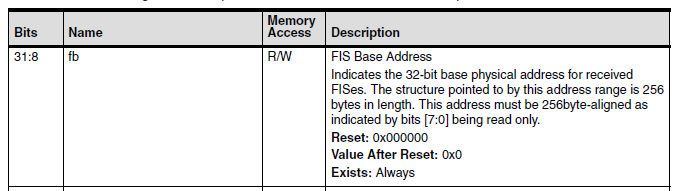

SATA在处理命令前构造的FIS和填充的数据都是存放在内存中,但是controller如何知道具体存放位置呢?这就要借助每个Port很重要的两个寄存器存放FIS(FB和FBS)的基地址和Command Header(CLB和CLBU)的基地址。

2.2.1 具体内存分配规则

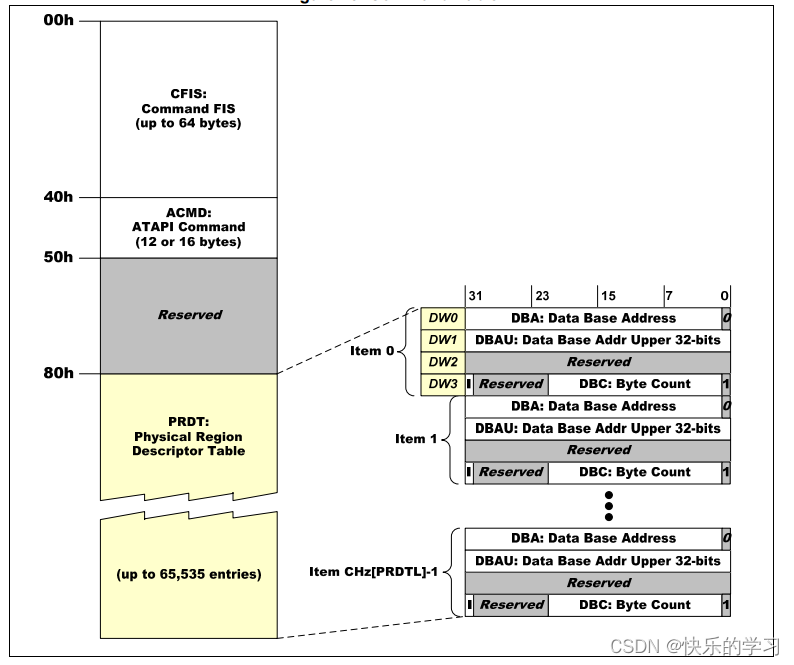

根据AHCI SPEC和sata驱动,每个port有一段分配的内存区域(CFIS)存放FIS内容和Comand List(PRDT)相关信息。

具体偏移地址如下:

if (pp->fbs_supported) {dma_sz = AHCI_PORT_PRIV_FBS_DMA_SZ;rx_fis_sz = ACARD_AHCI_RX_FIS_SZ * 16;} else {dma_sz = AHCI_PORT_PRIV_DMA_SZ;rx_fis_sz = ACARD_AHCI_RX_FIS_SZ; //512Byte}mem = dmam_alloc_coherent(dev, dma_sz, &mem_dma, GFP_KERNEL);if (!mem)return -ENOMEM;/** First item in chunk of DMA memory: 32-slot command table,* 32 bytes each in size*/pp->cmd_slot = mem;pp->cmd_slot_dma = mem_dma;mem += AHCI_CMD_SLOT_SZ; //32Byte * 32 command = 1024Bytemem_dma += AHCI_CMD_SLOT_SZ;/** Second item: Received-FIS area*/pp->rx_fis = mem;pp->rx_fis_dma = mem_dma;mem += rx_fis_sz; //512Byte 非FBS模式mem_dma += rx_fis_sz;/** Third item: data area for storing a single command* and its scatter-gather table*/pp->cmd_tbl = mem;pp->cmd_tbl_dma = mem_dma;

2.2.2 具体命令填充

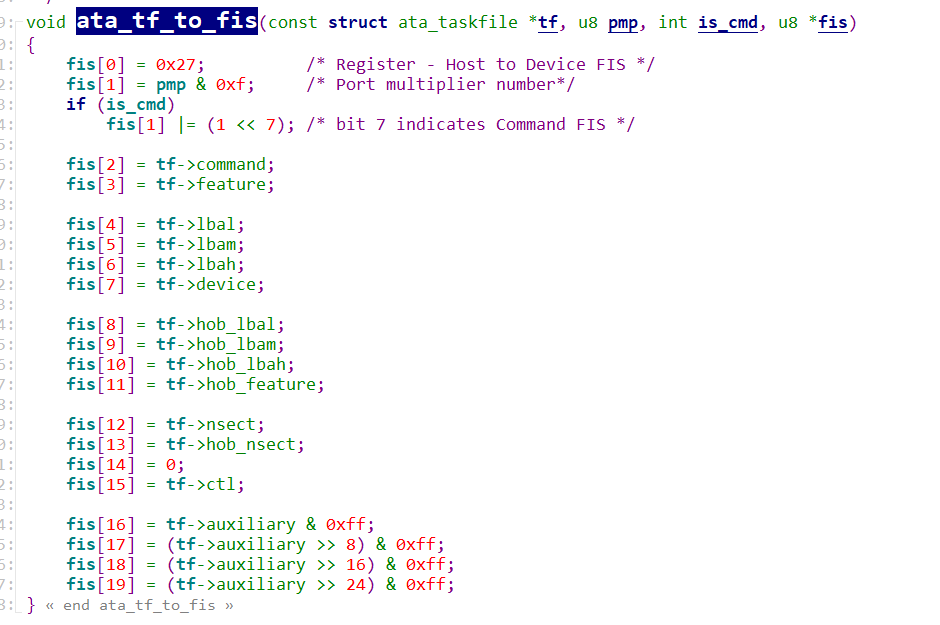

1、构造FIS填充在CFIS指定的地址

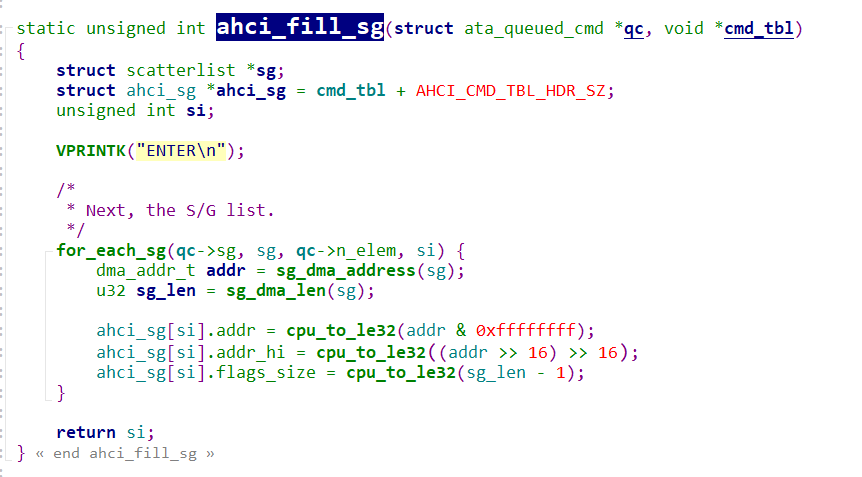

2、PRDT中一个sgl的地址,主要是数据传输时用来存放数据地址

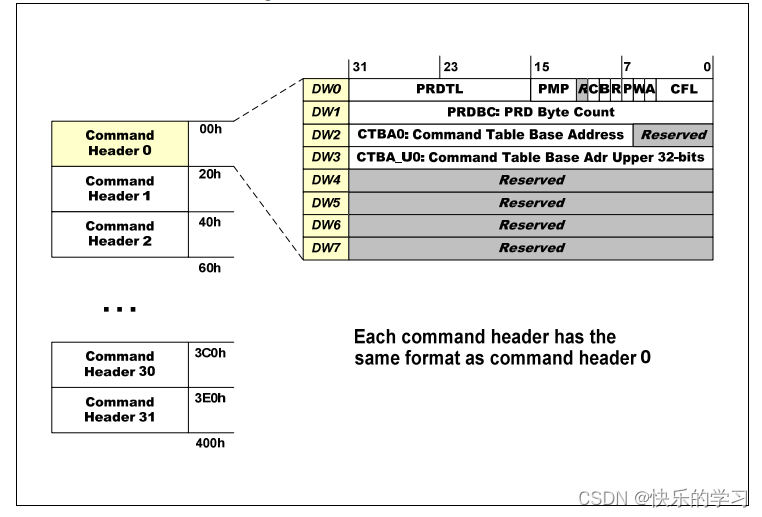

3、填充Command Header

每一个Port有32个Command Header,填充后Host或者Device根据顺序依次处理,每个Header填充了Comand Feature信息和Command Table的基地址,便于直接解析FIS和Command List。

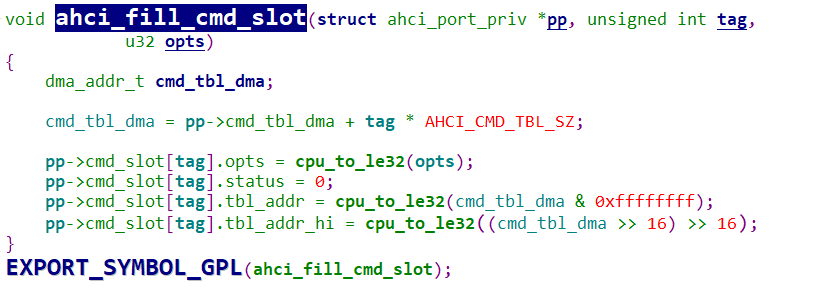

4、整体command构造代码流程如下

0-> ahci_qc_prep1-> ata_tf_to_fis //将tf的各个值填入到cfis中对应字段1-> memcpy(cmd_tbl + AHCI_CMD_TBL_CDB, qc->cdb, qc->dev->cdb_len); //如果是scsi的命令,则拷贝cdb命令到ACMD中,即使用SATA中的ATAPI命令。1-> ahci_fill_sg //将上层的sgl中的sg一个一个填入到PRD表中1-> ahci_fill_cmd_slot //填充command header,command header的地址初始化阶段已被写到了PxCLB和PxCLBU寄存器中2-> opts = cmd_fis_len | n_elem << 16 | (qc->dev->link->pmp << 12);opts |= AHCI_CMD_WRITE; //写命令opts |= AHCI_CMD_ATAPI | AHCI_CMD_PREFETCH; //atapi命令DW0=opts2-> 清零PRDBC,该字段用于当前已经完成的读写字节数2-> 将本命令的内存的DMA地址赋值给CTBA

2.2.3 命令触发流程

驱动在分配的对应的Command Header和Command Table内存并填充了相关信息后就要通知Host或者Device处理命令,具体流程如下:

1、填充分配给Command header Base地址到PnCLB和PnCLBU寄存器中;

2、填充FIS存放的BASE地址到PnFB和PnFBS中;

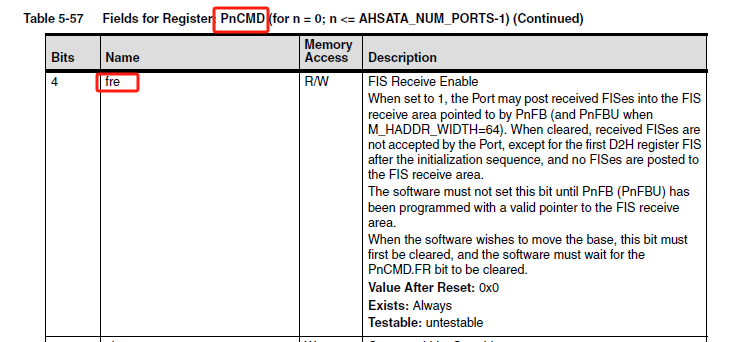

3、使能PnCMD中fre位使能FIS接收;

4、置位PnCI寄存器;

5、读PnTFD寄存器bit[7:0],确定command处理结果;

/* set FIS registers */if (hpriv->cap & HOST_CAP_64)writel((pp->cmd_slot_dma >> 16) >> 16,//将申请的cmd_slot_dma BASE地址写入到PnCLBport_mmio + PORT_LST_ADDR_HI);writel(pp->cmd_slot_dma & 0xffffffff, port_mmio + PORT_LST_ADDR);if (hpriv->cap & HOST_CAP_64)writel((pp->rx_fis_dma >> 16) >> 16,将申请的rx_fis_dma BASE地址写入到PnFBport_mmio + PORT_FIS_ADDR_HI);writel(pp->rx_fis_dma & 0xffffffff, port_mmio + PORT_FIS_ADDR);/* enable FIS reception */tmp = readl(port_mmio + PORT_CMD);tmp |= PORT_CMD_FIS_RX;writel(tmp, port_mmio + PORT_CMD);//使能FIS接收

/* issue & wait */writel(1, port_mmio + PORT_CMD_ISSUE); //通知处理command PnCIif (timeout_msec) {tmp = ata_wait_register(ap, port_mmio + PORT_CMD_ISSUE,0x1, 0x1, 1, timeout_msec);if (tmp & 0x1) {ahci_kick_engine(ap); //读取PnCMD中命令处理状态return -EBUSY;}} elsereadl(port_mmio + PORT_CMD_ISSUE); /* flush */return 0;

2.2.4 其他注意事项

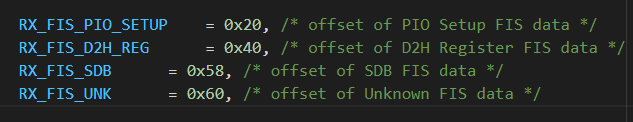

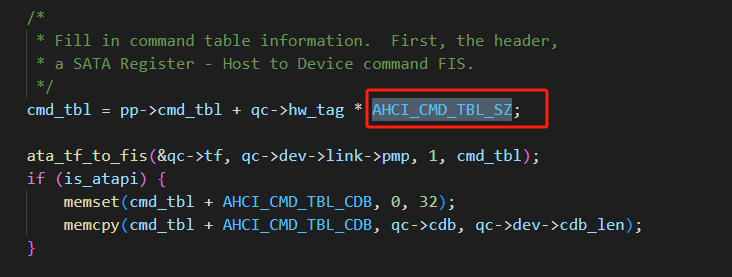

1、sata驱动中FB中填充的FIS BASEADDR(256Byte)存放FIS内容主要是PIO Setup FIS、D2H Register FIS、SDB FIS、Unknown FIS,而其他的FIS存放在Command Table中起始的位置,代码如下:

其他FIS存放起始地址:

cmd_tbl = pp->cmd_tbl + qc->hw_tag * AHCI_CMD_TBL_SZ;//Command Table起始地址ata_tf_to_fis(&qc->tf, qc->dev->link->pmp, 1, cmd_tbl);

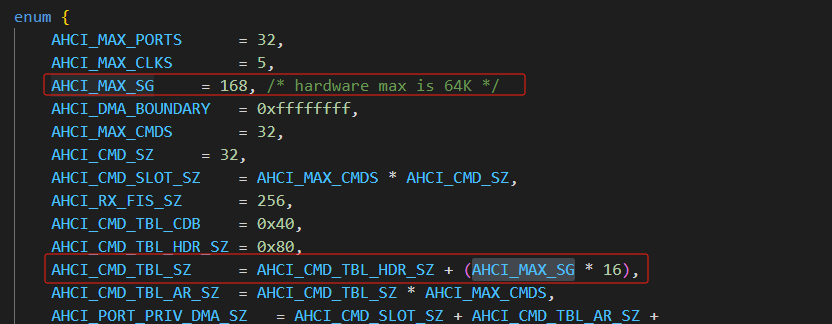

2、内核驱动中每个Port分配的Commad List数量有误

根据协议每个Command Table最大限制在1K对齐,硬件最大支持64K,而每个Command List为16B,则最大为64个,而内核驱动中写成168个,可能是开发人员手误多打了一个8:

相当于每个Table都额外多申请的内存:

具体的FIS类型参考博客链接:SATA信息传输FIS结构总结

三、其他相关链接

1、SATA模块之HBA卡开发总结(一)

2、SATA信息传输FIS结构总结

3、PCIe物理层总结-PCIE专题知识(一)

4、PCIe数据链路层图文总结-PCIe专题知识(二)

5、SSD硬盘SATA接口和M.2接口区别总结

这篇关于SATA驱动中FIS命令处理(详细)流程附代码和协议解析的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!