本文主要是介绍【上海大学数字逻辑实验报告】四、组合电路(三),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、 实验目的

- 掌握多路选择器74LS151的原理。

- 掌握译码器74LS138的原理。

- 学会在Quartus II上使用多路选择74LS151设计电路。

- 学会在Quartus II上使用译码器74LS138设计电路。

二、 实验原理

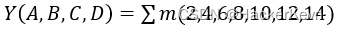

- 多路选择器又称数据选择器或多路开关,它是一种多路输入单路输出的组合逻辑电路,其逻辑功能是从多个输入中选出一个,并把它的信息传送到输出。输出对输入的选择受选择控制变量的控制。对于一个有2n个输入和一个输出的多路选择器,在n个选择控制信号作用下,把其中一个信号传送到输出端。本次实验使用的八选一选择器74151的逻辑符号如下图所示:

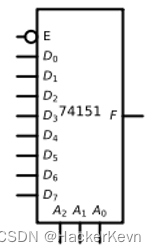

- 译码器是一种多输出组合逻辑部件,它能将n个输入变量变换成2n个输出函数,并且每个输出对应于n个输入变量的一个最小项。因此,二进制译码器具有n个输入端,2n个输出端和一个(或多个)使能输入端。本次实验使用的3线-8线译码器74138的逻辑电路图和逻辑符号如下图所示:

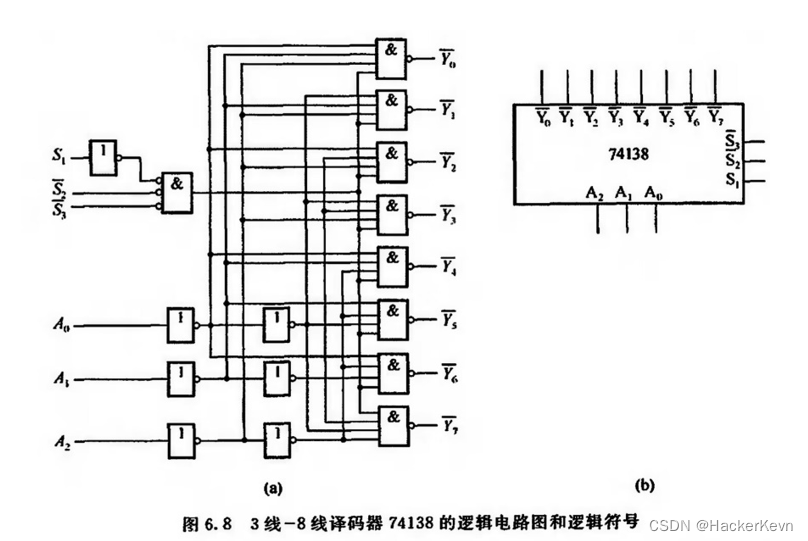

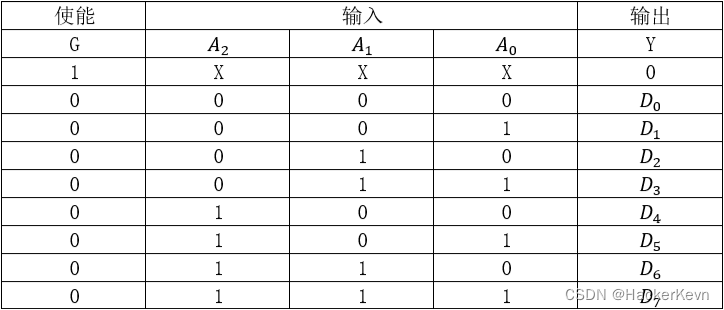

- 74138的真值表:

- 74151的真值表:

三、实验内容

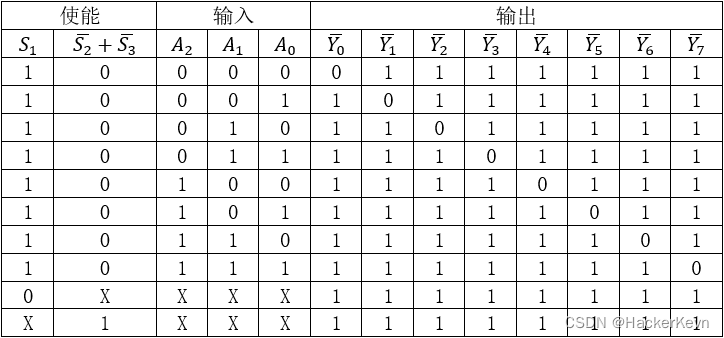

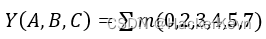

实验任务一:用多路选择器实现逻辑函数:

(1) 实验步骤

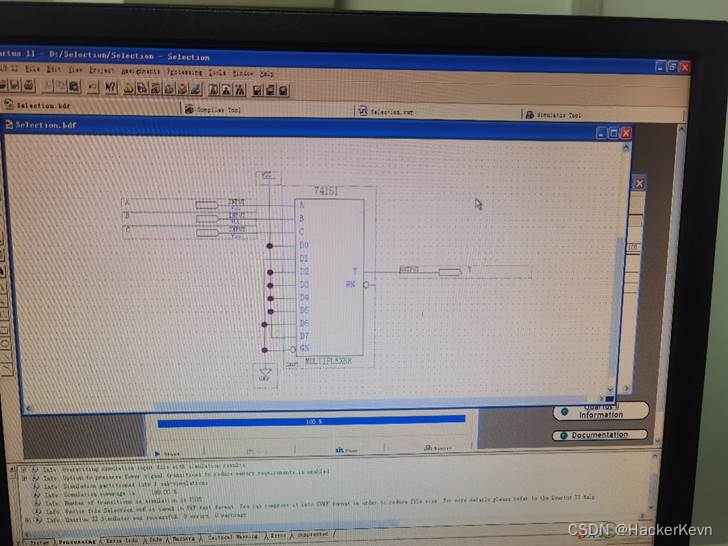

- 用Quartus II设计出如下电路:

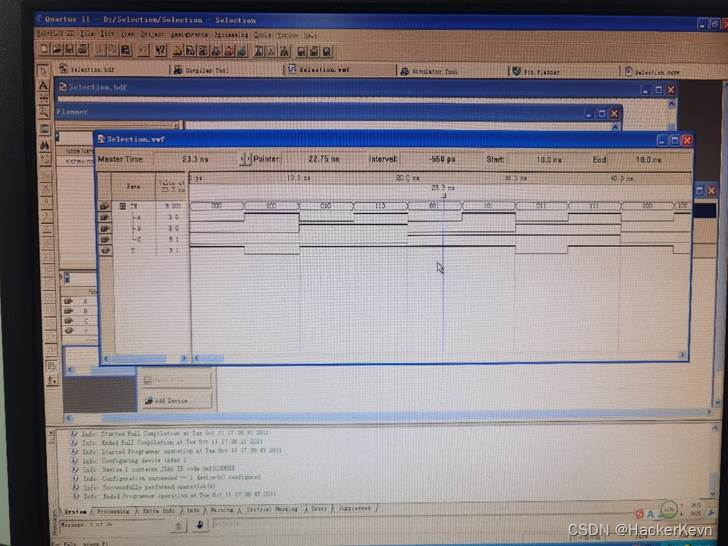

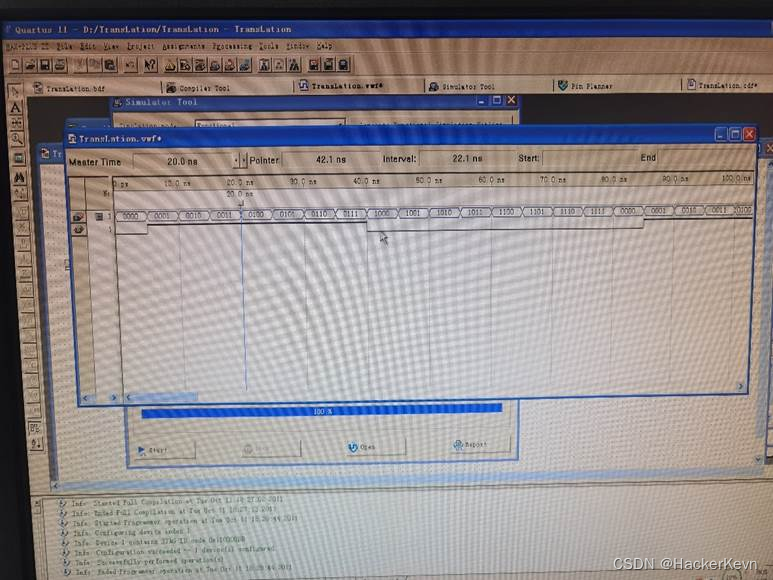

- 编译通过后进行波形仿真,验证电路逻辑功能:

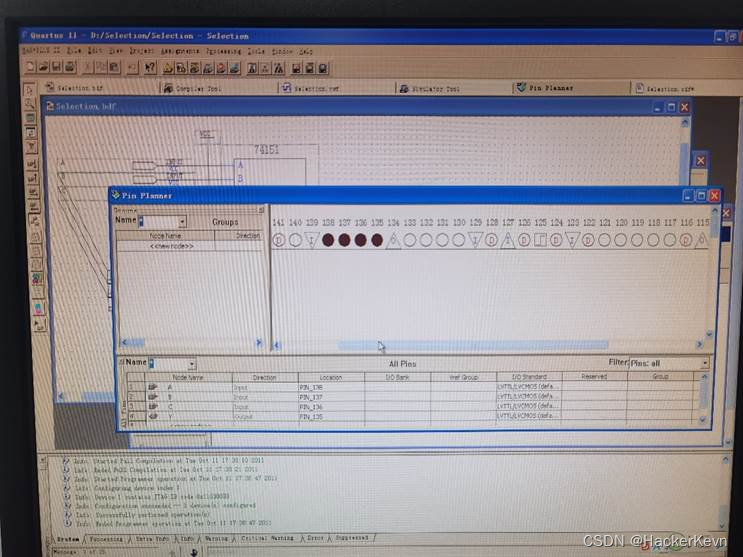

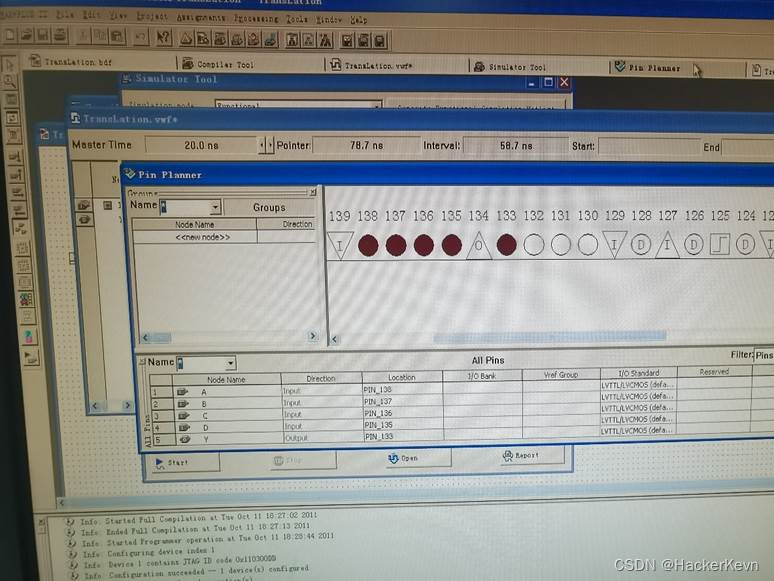

- 仿真通过后,参照原理图定义引脚:

- 生成编程并将文件下载到FPGA。

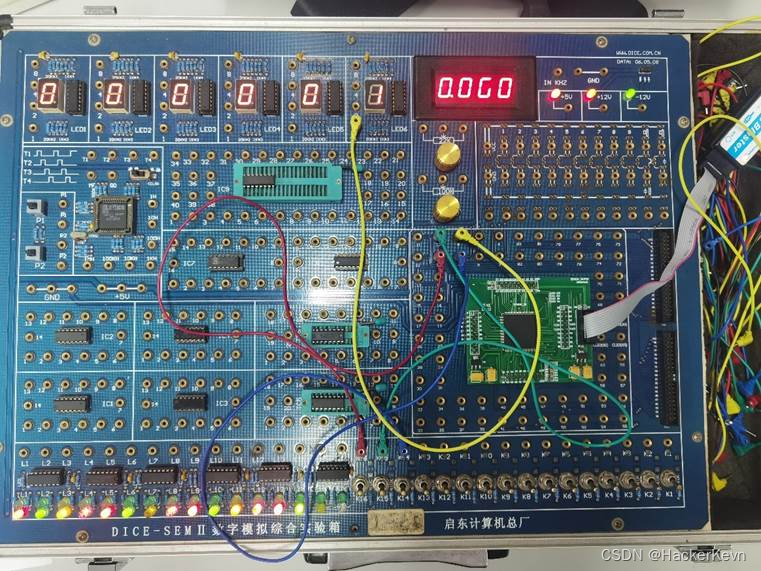

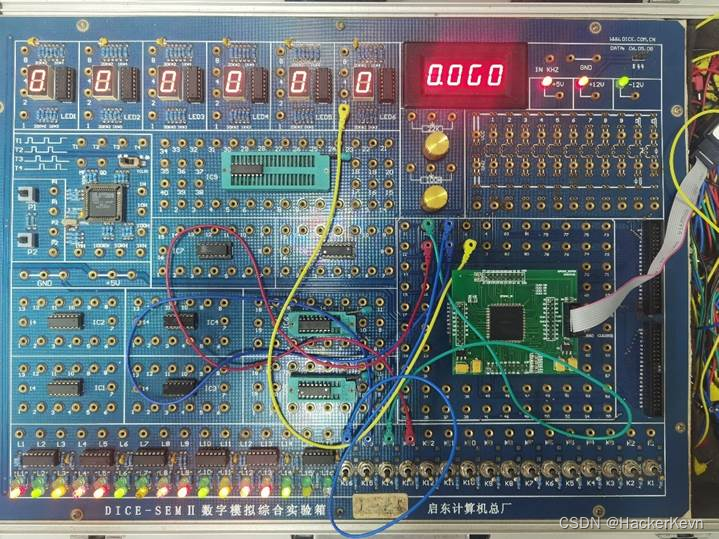

- 将开关连接对应的输入引脚,输出引脚连接到发光二极管:

- 用开关和发光二极管测试FPGA的功能。

- 记录测试结果。

(2) 实验现象

无论A0A1A2怎么输入,电路总是能根据逻辑函数输出对应的结果。

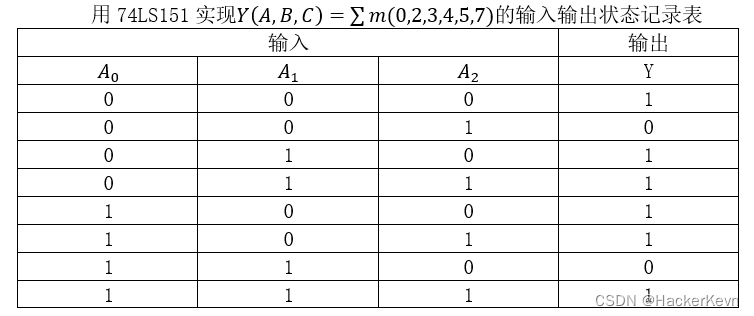

(3) 数据记录、分析与处理

(4) 实验结论

通过使用Quartus II设计工具,我们成功地用74LS151设计并测试了一个能够实现逻辑函数的电路。实验结果表明,电路在各种输入条件下都表现出良好的性能,符合预期行为。

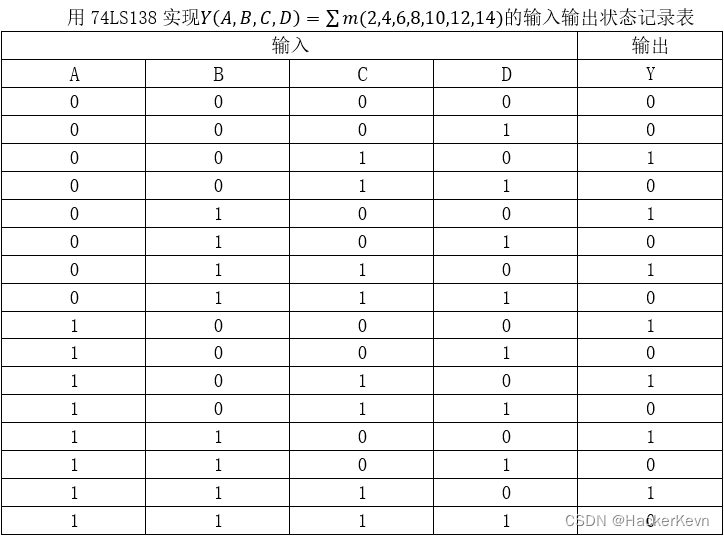

实验任务二:用译码器实现逻辑函数:

(1) 实验步骤

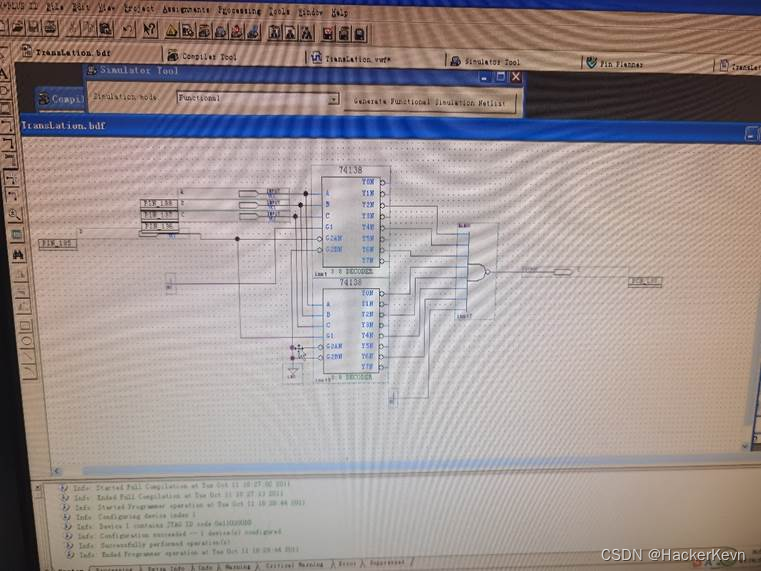

- 用Quartus II设计出如下电路:

- 编译通过后进行波形仿真,验证电路逻辑功能:

- 仿真通过后,参照原理图定义引脚:

- 生成编程并将文件下载到FPGA。

- 将开关连接对应的输入引脚,输出引脚连接到发光二极管:

- 用开关和发光二极管测试FPGA的功能。

- 记录测试结果。

(2) 实验现象

无论ABCD怎么输入,电路总是能根据逻辑函数输出对应的结果。

(3) 数据记录、分析与处理

(4) 实验结论

通过使用Quartus II设计工具,我们成功地用74LS138设计并测试了一个能够实现逻辑函数的电路。实验结果表明,电路在各种输入条件下都表现出良好的性能,符合预期行为。

四、建议和体会

- 在实验前,要理解并掌握用最小项表达逻辑函数的方法。

- 在设计电路时,注意接地。

- 将文件下载到FPGA后,接线时注意最低位和最高位不要接反。

- 不要一味用真值表的结果和波形模拟的结果进行对比,因为最高位最低位的顺序不同可能导致波形模拟的结果正好相反。

- 本实验有助于加深对多路选择器和译码器原理的理解,同时也提供了一个实际的编程和模拟测试经验。为后续进行更复杂的电路设计打下基础。

这篇关于【上海大学数字逻辑实验报告】四、组合电路(三)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!