本文主要是介绍数字IC基础:有符号数和无符号数加、减法的Verilog设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

相关阅读

数字IC基础![]() https://blog.csdn.net/weixin_45791458/category_12365795.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12365795.html?spm=1001.2014.3001.5482

本文是对数字IC基础:有符号数和无符号数的加减运算一文中的谈到的有符号数加减法的算法进行Verilog实现,有关算法细节请阅读原文,本文不会过多谈到原理相关问题。

虽然有符号加减和无符号加减在底层都是使用同样的补码加法器结构,但我们首先分别设计有符号加减法器和无符号加减法器,然后再将其组成一个完整的加减计算单元。

一个有符号数加减法器的Verilog描述如下所示。

//本加减法器不涉及-8作为减数的情况,-8作为减数需要单独讨论

module signed_adder(input signed [7:0]A, B, input mode, output reg signed [7:0]C, output reg OF);always@(*)beginif(mode == 0) begin //有符号加法C = A + B;OF = ((A[7] == B[7]) & (C[7] != A[7])); //溢出endelse begin //有符号减法C = A + (~B) +1'b1;OF = ((A[7] != B[7]) & (C[7] != A[7])); //溢出endend

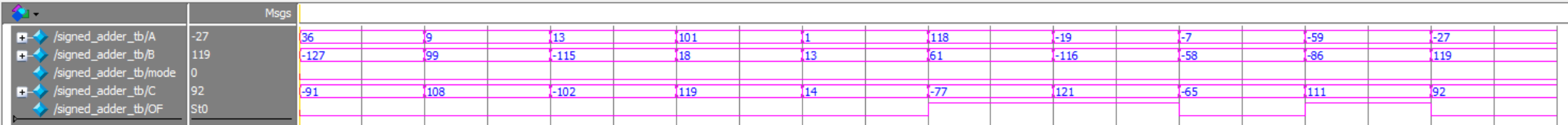

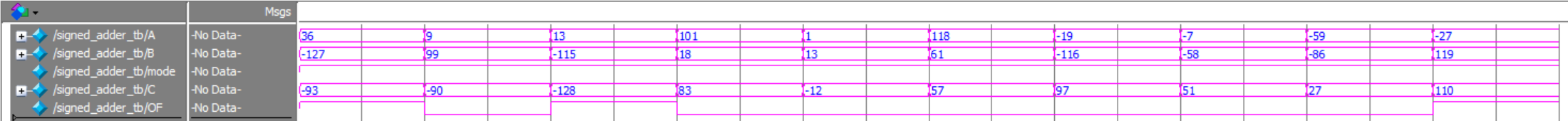

endmodule图1和图2是分别对加法和减法功能进行测试的波形,可以看出在某些情况下结果出现了溢出。

图1 有符号加法测试的波形

图2 有符号减法测试的波形

图2 有符号减法测试的波形

一个无符号加减法器的Verilog描述如下所示。

module unsigned_adder(input [7:0]A, B, input mode, output reg[7:0]C, output reg CF);reg cout;always@(*)beginif(mode == 0) begin //无符号加法{cout, C} = A + B;CF = cout; //进位endelse begin //无符号减法{cout, C} = A + (~B) +1'b1;CF = cout; //借位endend

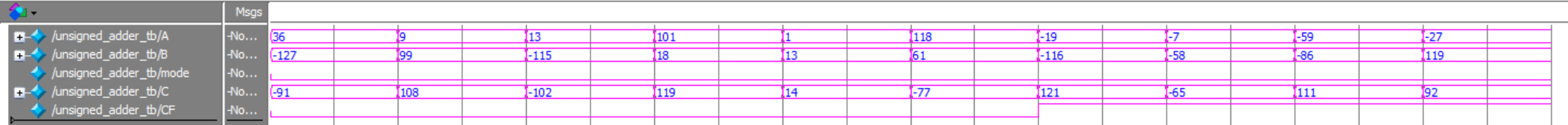

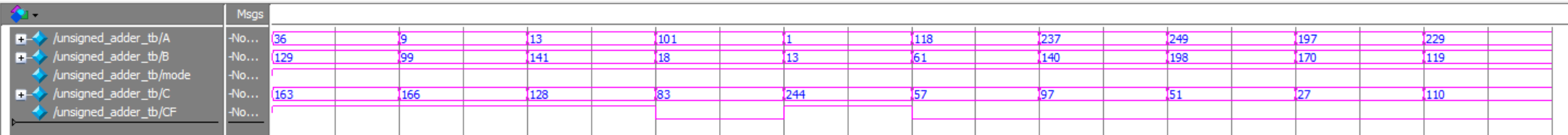

endmodule其中A和B会按照算法中谈到的一样,先补零拓展成9位数(这是自动进行的,进一步的位宽拓展问题可以阅读Verilog基础:表达式位宽的确定(位宽拓展)_verilog定义位宽-CSDN博客这篇文章),然后再按照有符号加减的运算。图3和图4是分别对加法和减法功能进行测试的波形,可以看出在某些情况下结果出现了进位和借位。

图3 无符号加法测试的波形

图3 无符号加法测试的波形

图4 无符号减法测试的波形

现在可以将两者结合,这样一个可以进行有符号数加减法和无符号数加减法的通用计算器就诞生了。

module adder(input [7:0]A, B, input mode, output reg[7:0]C, output reg CF);reg cout;always@(*)beginif(mode == 00) begin //有符号加法C = A + B;OF = ((A[7] == B[7]) & (C[7] != A[7])); //溢出endelse if(mode == 01) begin //有符号减法C = A + (~B) +1'b1;OF = ((A[7] != B[7]) & (C[7] != A[7])); //溢出endif(mode == 10) begin //无符号加法{cout, C} = A + B;CF = cout; //进位endelse if(mode == 11)begin //无符号减法{cout, C} = A + {(~B)} +1'b1;CF = !cout; //借位endend

endmodule下面是介绍有符号数和无符号数的加减运算的文章。

数字IC基础:有符号数和无符号数的加减运算![]() https://blog.csdn.net/weixin_45791458/article/details/134537623

https://blog.csdn.net/weixin_45791458/article/details/134537623

这篇关于数字IC基础:有符号数和无符号数加、减法的Verilog设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!