本文主要是介绍黑金AX7020开发板原理图学习分享第一部分 整体架构电源时序整理,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

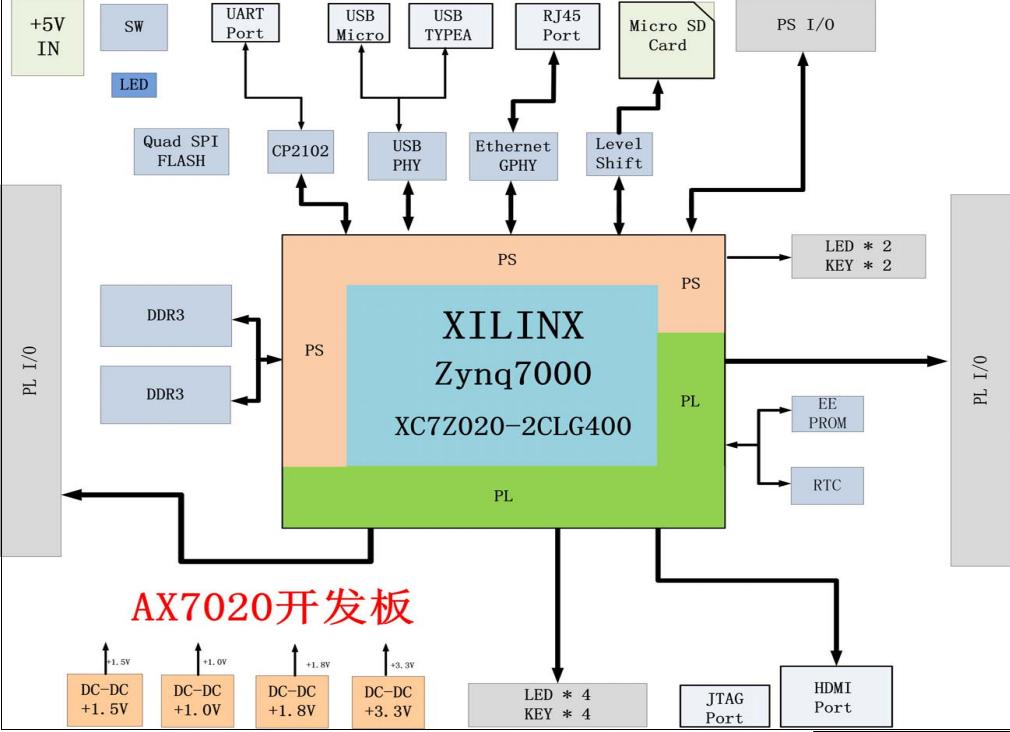

一 整体框图

图片为黑金官方提供原理框图

根据该框图可知:

1.主控芯片

开发板主控使用的是Zynq7000系列XC7020-2CLG400。

该芯片在赛灵思官网产品选型指南栏被规划至成本优化型产品,具体原因不清楚(笔者猜可能是因为较为节约成本)。

基于Xilinx SoC体系结构。集成了功能丰富的双核或单核ARM®Cortex™-A9处理系统(PS)和28 nm Xilinx可编程逻辑(PL)。

即可分成处理器系统部 Processor System(PS)和可编程逻辑部分 Programmable Logic(PL)。

BANK分布见下篇,具体功能分析。

2.板卡功能

1)两片大容量的 4Gbit(共 8Gbit)高速 DDR3 SDRAM,可作为 ZYNQ 芯片数据的缓存,也可以作为操作系统运行的内存;

2)一片 256Mbit 的 QSPI FLASH, 可用作 ZYNQ 芯片的系统文件和用户数据的存储;

3)一路 10/100M/1000M 以太网 RJ-45 接口, 可用于和电脑或其它网络设备进行以太网数据交换;

4)一路 HDMI 图像视频输入输出接口, 能实现 1080P 的视频图像传输;

5)一路高速 USB2.0 HOST 接口, 可用于开发板连接鼠标、键盘和 U 盘等 USB 外设;

6)一路高速 USB2.0 OTG 接口, 用于和 PC 或 USB 设备的 OTG 通信;

7)一路 USB Uart 接口, 用于和 PC 或外部设备的串口通信;

8)一片的 RTC 实时时钟,配有电池座,电池的型号CR1220。

9)一片 IIC 接口的 EEPROM 24LC04;

10)6 个用户发光二极管 LED, 2 个 PS 控制,4 个 PL 控制;

11)7 个按键,1 个 CPU 复位按键,2 个 PS 控制按键,4 个 PL 控制按键;

12)板载一个 33.333Mhz 的有源晶振,给 PS 系统提供稳定的时钟源,一个 50MHz 的有源晶振,为 PL 逻辑提供额外的时钟;

13)2 路 40 针的扩展口(2.54mm 间距),用于扩展 ZYNQ 的 PL 部分的 IO。可以接 7 寸 TFT模块、摄像头模块和 AD/DA 模块等扩展模块;

14)一个 12 针的扩展口(2.54mm 间距),用于扩展 ZYNQ 的 PS 系统的 MIO;

15)一路 USB JTAG 口,通过 USB 线及板载的 JTAG 电路对 ZYNQ 系统进行调试和下载。

16)1 路 Micro SD 卡座(开发板背面),用于存储操作系统镜像和文件系统。[1]

二 电源时序

盘一下子整个上电时序。

PS:建议VCCPINT(1.0V核电)、VCCPAUX(1.8V辅助电)和VCCPLL(PS端PLL1.8V电)同时供应。

然后PS VCCO供应VCCO_MIO0、VCCO_MIO1和VCCO_DDR。

VCC0_MIO0与VCCCO_MIO1选用的为1.8V电压模式而VCCO_DDR为1.5V供电,根据手册描述他们可由同电源同时供电。

PL端与PS端大致相同。

特别注意PL端注VCCO HR I/O与VCCAUX之间的电压差不得超过TVCCO2VCCAUX的2.625V,以保持设备的可靠性水平。已知两者稳定后压差1.5V,所以建议设计时采用同芯片同时上电。

AX7020电源设计为5V进电口进电,进电保险丝F3最大承载电流2A,整板功率不大于10W(板卡功率计算见下篇),然后由四片TLV62130RGT同时转出1V,1.8V,1.5V,3.3V。

VCCIO_35电源手册没找到,看着是一部分给FPGA一部分用作灯和按键的开关了,等找到引脚手册看一下,下一篇介绍。

赛灵思原文上电时序描述:

PS:The recommended power-on sequence is VCCPINT, VCCPAUX and VCCPLL together, then the PS VCCO supplies (VCCO_MIO0,VCCO_MIO1, and VCCO_DDR) to achieve minimum current draw and ensure that the I/Os are 3-stated at power-on. The recommended power-off sequence is the reverse of the power-on sequence. If VCCPAUX, VCCPLL and the PS VCCO supplies (VCCO_MIO0, VCCO_MIO1, and VCCO_DDR) have the same recommended voltage levels, then they can be powered by the same supply and ramped simultaneously. Xilinx recommends powering VCCPLL with the same supply as VCCPAUX, with an optional ferrite bead filter.

PL:The recommended power-on sequence for the PL is VCCINT, VCCBRAM, VCCAUX, and VCCO to achieve minimum current draw and ensure that the I/Os are 3-stated at power-on. The recommended power-off sequence is the reverse of the power-on sequence. If VCCINT and VCCBRAM have the same recommended voltage levels then both can be powered by the same supply and ramped simultaneously. If VCCAUX and VCCO have the same recommended voltage levels then both can be powered by the same supply and ramped simultaneously.

For VCCO voltages of 3.3V in HR I/O banks and configuration bank 0:

• The voltage difference between VCCO and VCCAUX must not exceed 2.625V for longer than TVCCO2VCCAUX for each power-on/off cycle to maintain device reliability levels.

• The TVCCO2VCCAUX time can be allocated in any percentage between the power-on and power-off ramps

[2]

令附赛灵思官方电源手册及开发板原理图资料链接:

链接:https://pan.baidu.com/s/10Ml7sP-mTRhuQWqVgV0JJQ

提取码:uk9t

PS:边学边写,不喜勿喷,发现错误欢迎批评指正。

注:

[1]摘自《cource_s1_ALINX_ZYNQ(AX7010_AX7020)2019版开发平台FPGA教程V1.02》。

[2]摘自《ds187-XC7Z010-XC7Z020-Data-Sheet》。

这篇关于黑金AX7020开发板原理图学习分享第一部分 整体架构电源时序整理的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!