本文主要是介绍【FGPA】Verilog:移位寄存器 | 环形计数器 | 4bit移位寄存器的实现 | 4bit环形计数器的实现,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

Ⅰ. 理论部分

0x00 移位寄存器(Shift Register)

0x01 环形计数器(Ring Counter)

Ⅱ. 实践部分

0x00 移位寄存器(4-bit)

0x01 四位环形寄存器(4-bit)

Ⅰ. 理论部分

0x00 移位寄存器(Shift Register)

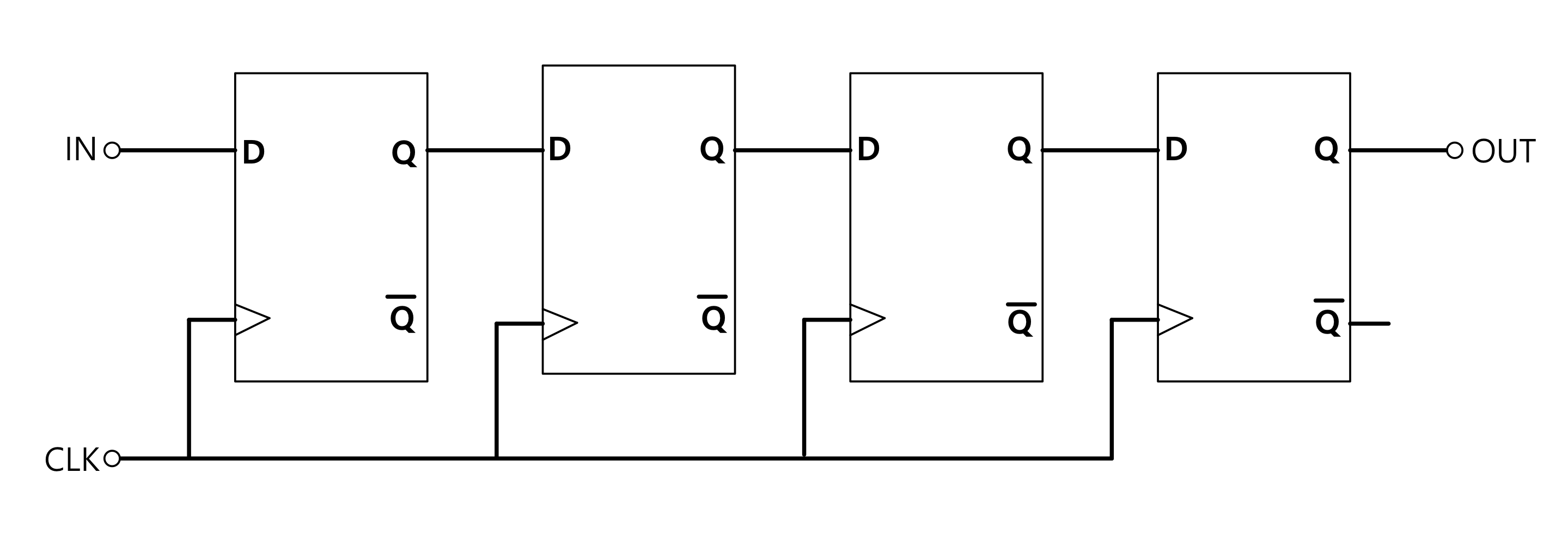

移位寄存器 (Shift Register) 是 由多个触发器串联连接而成的形式,其中一个触发器的输出传递到下一个触发器的输入。它与上周调查的异步计数器具有相似的形式。因此,存储在触发器的内存中的值在时钟更新时每次向右移动一位。新的数据值从输入线存储到左侧的存储器中。

| 移位寄存器(Shift Register) |

|

|

0x01 环形计数器(Ring Counter)

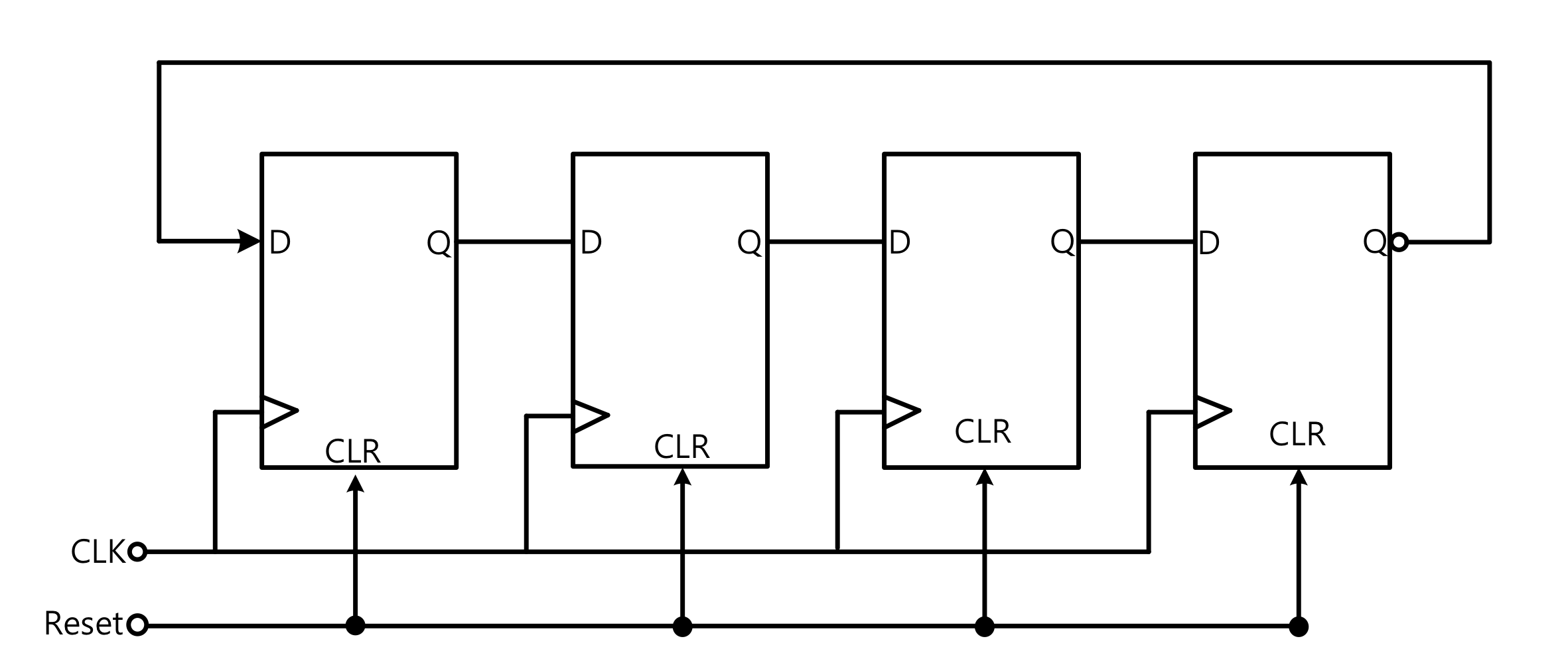

环形计数器 (Ring Counter) 是一种 以数据在一系列中旋转的形式存储的移位寄存器。 最后一个触发器的输出连接到第一个触发器的输入,形成一个类似 "圆环" 的形状,因此被称为环形计数器。输入的数据在每个时钟脉冲下移动一格,是串行通信电路的基础电路。

环形计数器是由移位寄存器加上一定的反馈电路构成的,用移位寄存器构成环形计数器的一般框图,它是由一个移位寄存器和一个组合反馈逻辑电路闭环构成,反馈电路的输出接向移位寄存器的串行输入端,反馈电路的输入端根据移位寄存器计数器类型的不同,可接向移位寄存器的串行输出端或某些触发器的输出端。

| 环形计数器(Ring Counter) |

|

|

Ⅱ. 实践部分

0x00 移位寄存器(4-bit)

📚 请描述 4 位移位寄存器的结果和仿真过程。用 Verilog 实现 4 位移位寄存器,画出移位寄存器输出表,并在 Verilog 中验证仿真结果。

📃 输出表如下:

💬 Source Code:

`timescale 1ns / 1psmodule SR(input reset,input clk,input x,output[3:0] out

);reg[3:0] out;always @(posedge clk) beginif(reset) beginout[3] <= 1'b0;out[2] <= 1'b0;out[1] <= 1'b0;out[0] <= 1'b0;endelse beginif((x == 1'b1)) beginout[3] <= 1'b1;out[2] <= out[3];out[1] <= out[2];out[0] <= out[1];endelse beginout[3] <= 1'b0;out[2] <= out[3];out[1] <= out[2];out[0] <= out[1];endendendendmodule💬 Testbench:

`timescale 1ns / 1psmodule SR_tb;reg clk,reset,x;

wire[3:0] out;SR u_SR(.clk(clk ),.reset(reset ),.x(x ),.out(out )

);initial clk = 1'b0;

initial reset = 1'b1;

initial x = 1'b0;always clk = #20 ~clk;always@(reset) beginreset = #30 ~reset;

endalways@(x) beginx = #50 ~x;x = #20 ~x;x = #60 ~x;x = #20 ~x;x = #20 ~x;x = #20 ~x;

endinitial begin#380$finish;

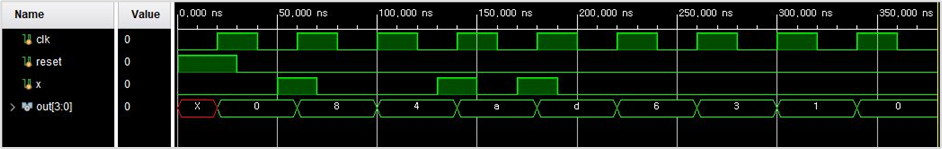

endendmodule🚩 运行结果如下:

💡 分析:每当时钟发生转换 (clock transition) 时,移位寄存器就会将存储的值向右推进一个空格(LSB 方向),新输入数据的值则存储在左侧(MSB)。该电路采用上升沿触发器 (rising edge trigger) 设计,因此当时钟值从 0 变为 1 时,状态变化就会应用到存储器中。因此,在每次时钟转换时,我们都会执行一个操作,将新输入数据的值存储在 MSB 位,同时执行一个操作,将存储在 4 位存储器中的值向 LSB 位移动一个空格。

0x01 四位环形寄存器(4-bit)

📚 请描述 4 位唤醒寄存器的结果和仿真过程。用 Verilog 实现 4 位环形寄存器,画出移位寄存器输出表,并在 Verilog 中验证仿真结果。

📃 输出表如下:

💬 Source Code:

`timescale 1ns / 1psmodule RC(input reset,input clk,output[3:0] out

);reg[3:0] out = 4'b1000;always @(posedge clk) beginif(reset) beginout[3] <= 1'b0;out[2] <= 1'b0;out[1] <= 1'b0;out[0] <= 1'b0;endelse beginout[3] <= out[0];out[2] <= out[3];out[1] <= out[2];out[0] <= out[1];endendendmodule💬 Testbench:

`timescale 1ns / 1psmodule RC_tb;reg clk,reset;

wire[3:0] out;RC u_RC(.clk(clk ),.reset(reset ),.out(out )

);initial clk = 1'b0;

initial reset = 1'b0;always clk = #20 ~clk;always@(reset) beginreset = #330 ~reset;reset = #20 ~reset;

endinitial begin#380$finish;

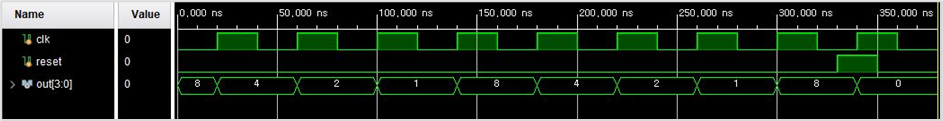

endendmodule🚩 运行结果如下:

💡 分析:每次时钟转换时,环形计数器都会将存储的数值向右(LSB 方向)推进一个空格。这种行为与移位寄存器类似,只是没有新的输入数据值。不过,对于环形计数器,设计时应使 LSB 的值返回到 MSB,这样内存中存储的四个比特的总值就会循环。电路采用上升沿触发器设计,因此当时钟值从 0 变为 1 时,当前状态的变化将被应用到存储器中。因此,每当时钟转换一次,存储在存储器 4 位中的值就会被推到 LSB 位存储一个空格,但 LSB 位中的值又会被存储到 MSB 位,仿真结果表明,它与真值表一样有效。

📌 [ 笔者 ] 王亦优

📃 [ 更新 ] 2023.11.10

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |

这篇关于【FGPA】Verilog:移位寄存器 | 环形计数器 | 4bit移位寄存器的实现 | 4bit环形计数器的实现的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!