本文主要是介绍基于FPGA的DVP协议实现标准图像数据流转换(OV7670摄像头),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

一、什么是DVP?

二、OV7670摄像头的DVP协议时序

三、RTL设计

一、什么是DVP?

DVP(Digital Video Port) 是传统的sensor输出接口,采用并行输出方式,d数据位宽有8bit、10bit、12bit、16bit,是CMOS电平信号(重点是非差分信号),PCLK最大速率为96MHz,接口如下图:

PCLK:pixel clock ,像素时钟,每个时钟对应一个像素数据;

HSYNC:horizonal synchronization,行同步信号

VSYNC:vertical synchronization,帧同步信号;

DATA:像素数据,视频数据,具体位宽要看ISP是否支持;

XCLK:或者MCLK,ISP芯片输出给驱动sensor的时钟;

SCL,SDA:IIC用来读写sensor的寄存器,配置sensor。

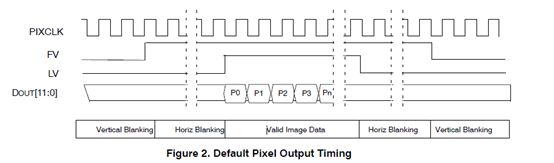

DVP协议是摄像头中常用的协议,除了DVP协议摄像头中还有其他常用的协议如:MIPI、LVDS等协议。其整体协议时序图如图:

图中PIXCLK信号即是PCLk信号,FV是帧同步信号,LV是行同步信号,输出的P0~Pn就是像素数据。

二、OV7670摄像头的DVP协议时序

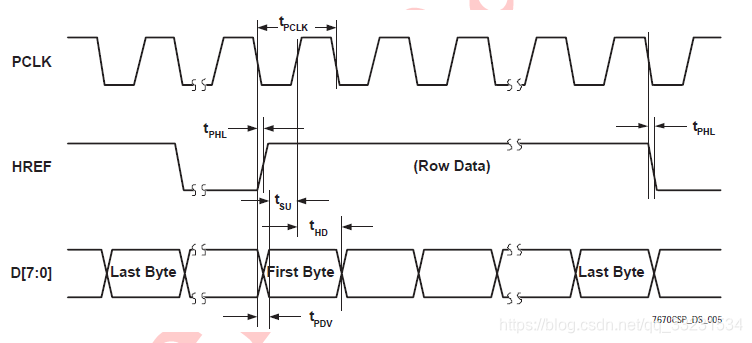

(1)水平时序

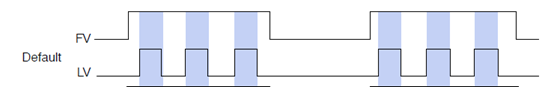

(2)和VGA对应的帧时序

DVP协议和VGA接口协议基本一样,只是VSYNC信号高低电平相反了。还有DVP协议的HREF信号是在HERF为高电平是直接输出像素数据,而VGA接口的HSYNC信号在HSYNC为高时先后输出显示后沿、有效图像数据、显示前沿。

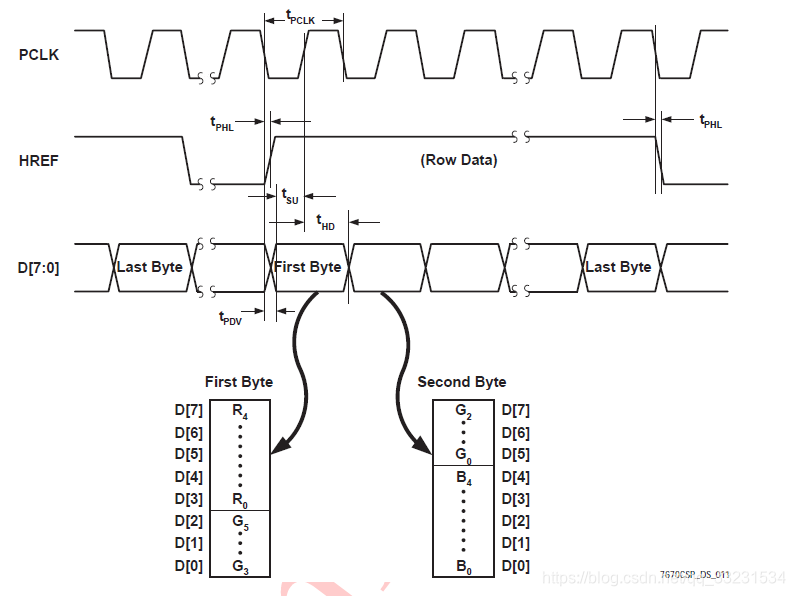

(3)这里对OV7670摄像头配置输出的是RGB565图像数据,其时序为:

(4)配置成RGB555和RGB444输出时序如图:

三、RTL设计

从上边所看的时序图可以将DVP协议转换成标准的图像的数据流,代码如下:

// Company :

// Engineer :

// -----------------------------------------------------------------------------

// https://blog.csdn.net/qq_33231534 PHF's CSDN blog

// -----------------------------------------------------------------------------

// Create Date : 2020-09-24 22:17:57

// Revise Data : 2020-09-24 22:17:57

// File Name : ov7670_data_16rgb565.v

// Target Devices : XC7Z015-CLG485-2

// Tool Versions : Vivado 2019.2

// Revision : V1.1

// Editor : sublime text3, tab size (4)

// Description : DVP协议(digital video port)获取ov7670数据并转换成16位RGB565图像数据module ov7670_data_16rgb565(input clk ,//输入为摄像头输入时钟pclk 25MHzinput rst_n ,//系统复位input vsync ,//场同步信号input href ,//行同步信号input [7:0] din ,//ov7670摄像头数据输入input init_done ,//ov7670摄像头初始化结束标志output reg[15:0] data_rgb565 ,//转换成16位RGB565图像数据output reg data_rgb565_vld //16位RGB565图像数据有效标志);reg vsync_r ;reg href_r ;reg [7:0] din_r ;reg vsync_r_ff0 ;reg vsync_r_ff1 ;reg data_start ;reg [3:0] frame_cnt ;reg frame_vaild ;wire vsync_r_pos ;reg data_en ;//外部信号打一拍always @(posedge clk or negedge rst_n) beginif (!rst_n) beginvsync_r <= 0;href_r <= 0;din_r <= 8'd0;endelse beginvsync_r <= vsync;href_r <= href;din_r <= din;endend//场同步信号上升沿检测always @(posedge clk or negedge rst_n) beginif (!rst_n) beginvsync_r_ff0 <= 0;vsync_r_ff1 <= 0;endelse beginvsync_r_ff0 <= vsync_r;vsync_r_ff1 <= vsync_r_ff0;endendassign vsync_r_pos = (vsync_r_ff0 && ~vsync_r_ff1);always @(posedge clk or negedge rst_n) beginif (!rst_n) begindata_start <= 0;endelse if (init_done) begindata_start <= 1;endelse begindata_start <= data_start;endendalways @(posedge clk or negedge rst_n) beginif (!rst_n) beginframe_cnt <= 0;endelse if (data_start && frame_vaild==0 && vsync_r_pos) beginframe_cnt <= frame_cnt + 1'b1;endelse beginframe_cnt <= frame_cnt;endendalways @(posedge clk or negedge rst_n) beginif (!rst_n) beginframe_vaild <= 0;endelse if (frame_cnt >= 10) beginframe_vaild <= 1;endelse beginframe_vaild <= frame_vaild;endendalways @(posedge clk or negedge rst_n) beginif (!rst_n) begindata_en <= 0;endelse if (href_r && frame_vaild) begindata_en <= ~data_en;endelse begindata_en <= 0;endendalways @(posedge clk or negedge rst_n) beginif (!rst_n) begindata_rgb565_vld <= 0;endelse if (data_en) begindata_rgb565_vld <= 1;endelse begindata_rgb565_vld <= 0;endendalways @(posedge clk or negedge rst_n) beginif (!rst_n) begindata_rgb565 <= 16'd0;endelse if (data_en) begindata_rgb565 <= {data_rgb565[15:8],din_r};endelse begindata_rgb565 <= {din_r,data_rgb565[7:0]};endendendmodule

测试代码:

`timescale 1ns/1nsmodule ov7670_data_16rgb565_tb (); /* this is automatically generated */reg rst_n;reg clk;localparam clk_period = 20;reg vsync;reg href;reg [7:0] din;reg init_done;wire [15:0] data_rgb565;wire data_rgb565_vld;ov7670_data_16rgb565 inst_ov7670_data_16rgb565(.clk (clk),.rst_n (rst_n),.vsync (vsync),.href (href),.din (din),.init_done (init_done),.data_rgb565 (data_rgb565),.data_rgb565_vld (data_rgb565_vld));initial clk = 1;always #(clk_period/2) clk = ~clk;initial begin#2;rst_n = 0;vsync = 0;href = 0;din = 0;init_done = 0;#(clk_period*20);rst_n = 1;#(clk_period*20);init_done = 1;#clk_period;init_done = 0;#(clk_period*20);repeat(12)begin#(clk_period*500);dvp_data();end#(clk_period*20);$stop;endtask dvp_data;integer i,j;beginvsync = 0;#(clk_period*10);vsync = 1;#(clk_period*10);vsync = 0;#(clk_period*100);for(i=0;i<480;i=i+1)beginfor(j=0;j<640*2;j=j+1)beginhref = 1;#(clk_period);din = din + 1'b1;endhref = 0;#(clk_period*100);enddin = 0;endendtaskendmodule

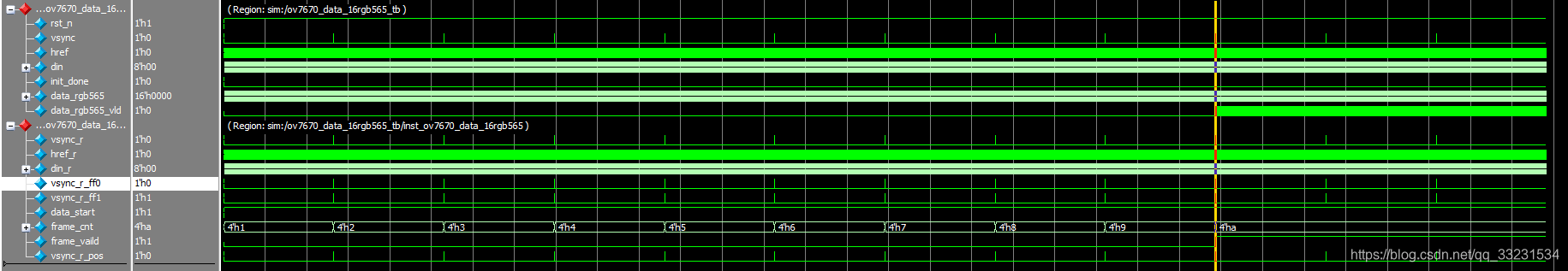

仿真图如图所示:

(1)传输12帧图像数据

可以看到,data_rgb565_vld数据有效信号在10帧图像数据后才有输出,这是为了在初始化后图像数据可能会有不稳定情况,因此将前十帧图像丢弃。

(2)1帧图像数据(注意看帧同步信号)

(3)传输数据部分细节

这篇关于基于FPGA的DVP协议实现标准图像数据流转换(OV7670摄像头)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!