本文主要是介绍AD9371 官方例程HDL详解之JESD204B RX侧时钟生成,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

AD9371 系列快速入口

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成(一)

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (二)

采样率和各个时钟之间的关系 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (三)

参考资料:

UltraScale Architecture GTH Transceivers User Guide UG576

Generic JESD204B block designs

文章目录

- 前言

- 一、RXOUTCLK

- 二、RX Serial Clock 和 PMA Parallel Clock

- 三、RX 和 RX_OS 的 LaneRate

- 四、AD9371官方例程 RXOUTCLK、 RXUSRCLK 和 RXUSRCLK2

前言

RX侧 RXUSRCLK、 RXUSRCLK2、25 MHz clock 和TX基本相同

一、RXOUTCLK

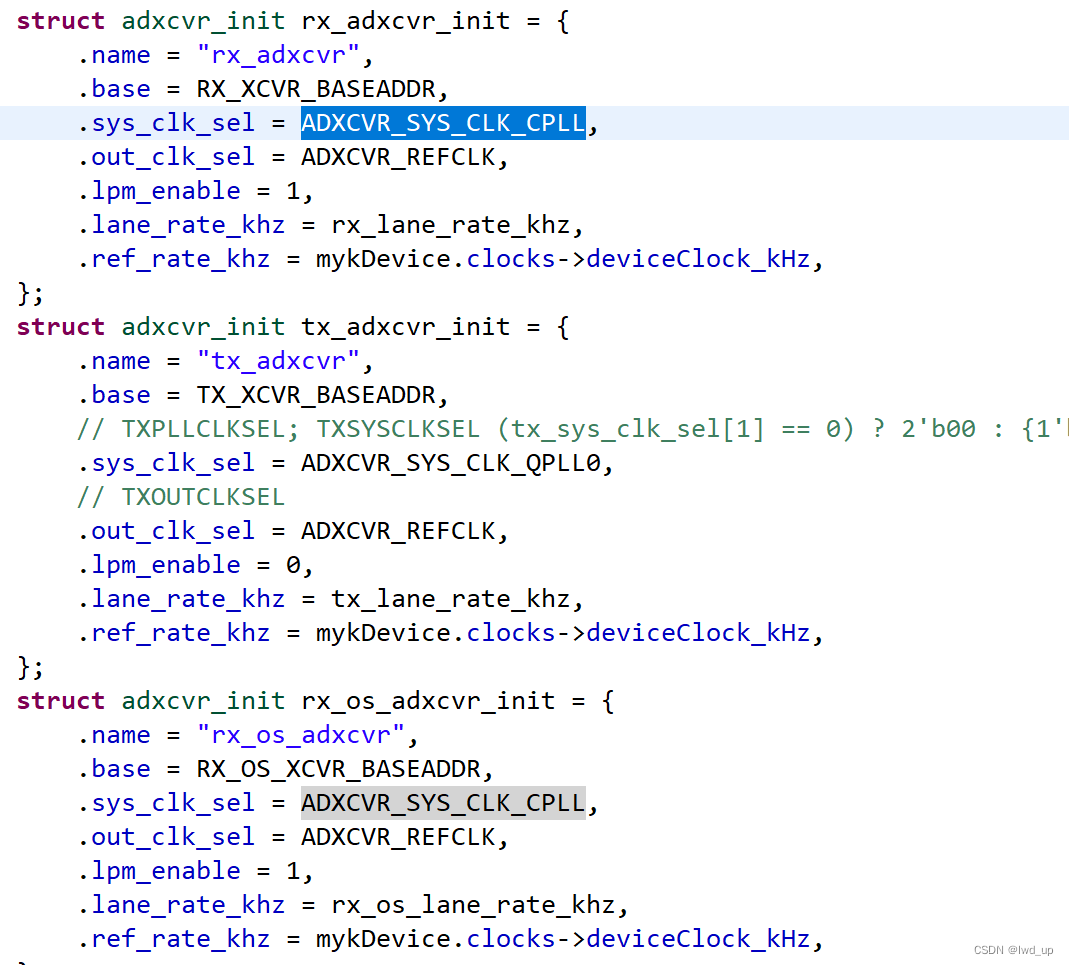

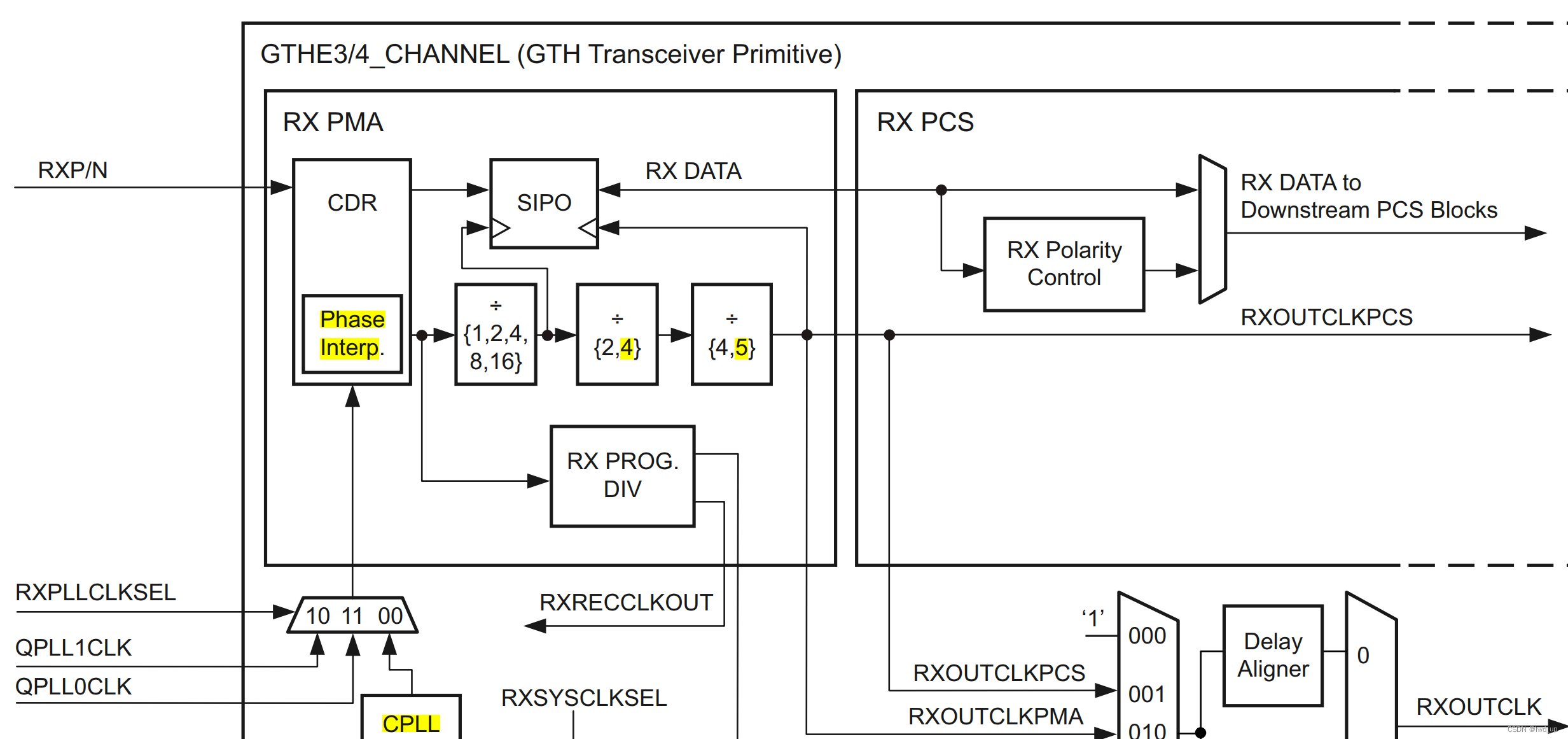

RXOUTCLK 经过 BUFG_GT后 驱动RXUSRCLK2和RXUSRCLK ,RXOUTCLK 可以根据 RXOUTCLKSEL 选择来源,根据下述程序 RXOUTCLK = 3’b011; 选择 RXPLLREFCLK_DIV1

sys_clk_sel = ADXCVR_SYS_CLK_CPLL=0;

RXOUTCLK 来自于 CPLL 的参考时钟,可知 QPLL0、 QPLL1、 CPLL的参考时钟 都是 MGTREFCLK 通过 IBUFDS_GTE4后提供到channel 的 GTREFCLK0,即 ref_clk1,AD9528 的 OUT1,RXOUTCLK 来源于AD9528 的 OUT1 。

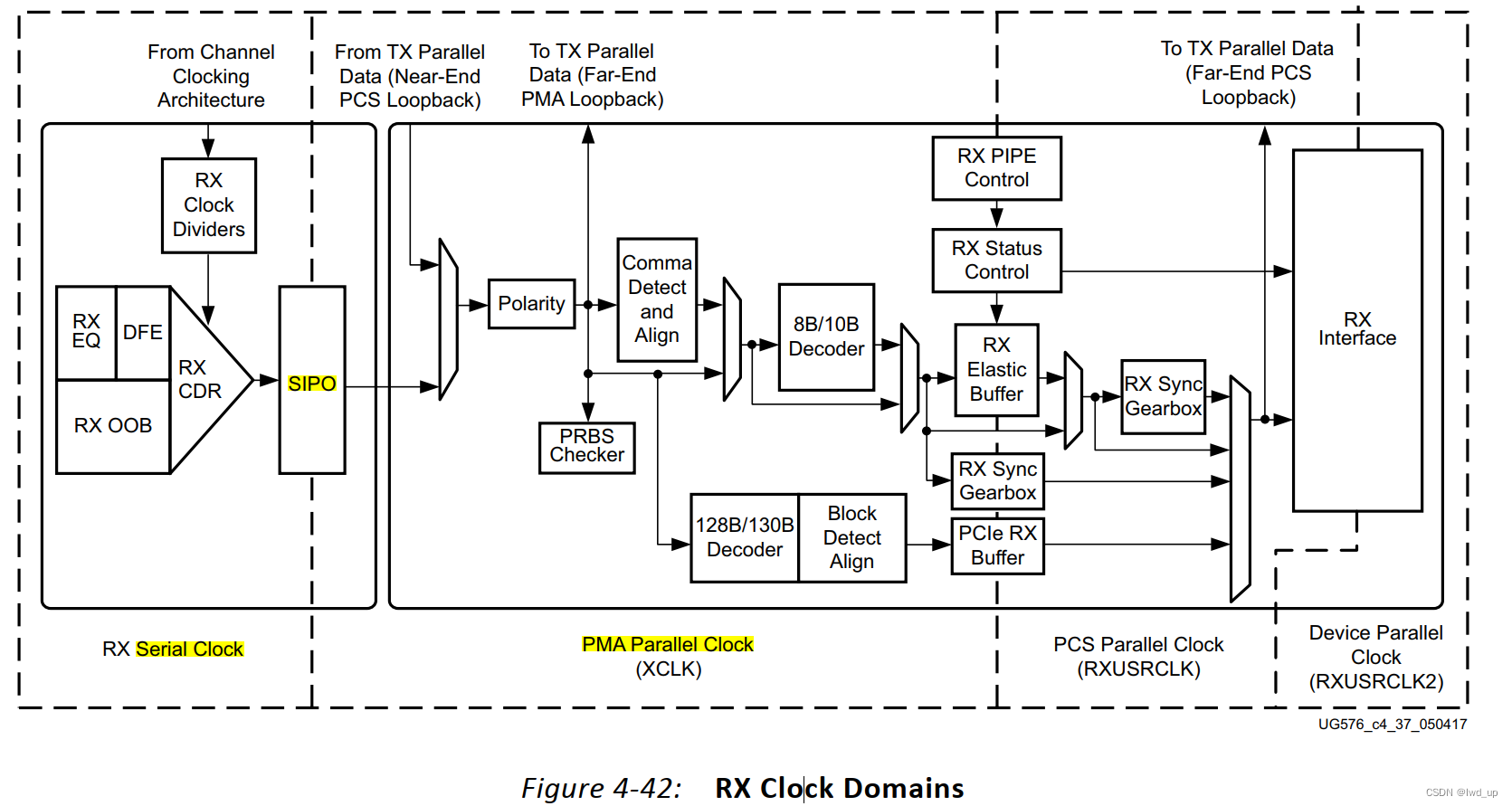

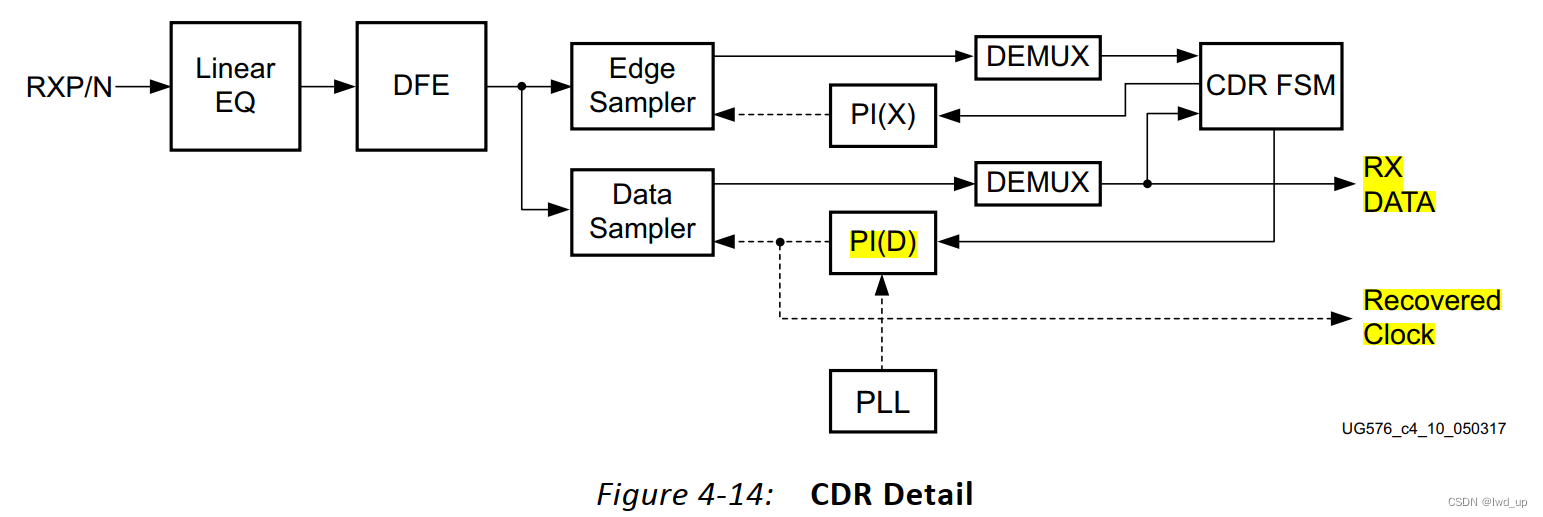

二、RX Serial Clock 和 PMA Parallel Clock

RX Serial Clock 是利用 RX 相位插值 CDR, 从接收数据中恢复出的串行时钟

PMA Parallel Clock 是恢复出的高速时钟经过 串行 并行分频器后得到的, PMA Parallel Clock 和 后续的 RXUSRCLK、 RXUSRCLK2 时钟不在一个时钟域 ,需要 RX Elastic Buffer跨时钟域

三、RX 和 RX_OS 的 LaneRate

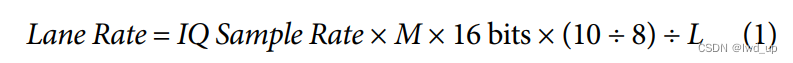

rx_lane_rate 和 采样率之间的关系

M是有几个转换器,每个采样数据是16 bit,经过8B/10B编码到 20bit , L是有几个LANE传数据

RX中,demo中 2T2R,M=4(1发 需要IQ 两路转换器), L=2(demo 分配2个LANE ) 的情况下 ,根据IQ rate(122.88M) 可以求得所需的RxLineRate(4915.2 MHz)

IQRate = R x L i n e R a t e 40 \text {IQRate }=\frac{{RxLineRate} }{40} IQRate =40RxLineRate

对于 RX_OS, M=2(观察或者嗅探采样器), L=2(demo 分配2个LANE ) 的情况下 ,根据IQ rate(122.88M) 可以求得所需的RxOSLineRate(2457.6 MHz)

IQRate = R x O S L i n e R a t e 20 \text {IQRate }=\frac{{RxOSLineRate} }{20} IQRate =20RxOSLineRate

四、AD9371官方例程 RXOUTCLK、 RXUSRCLK 和 RXUSRCLK2

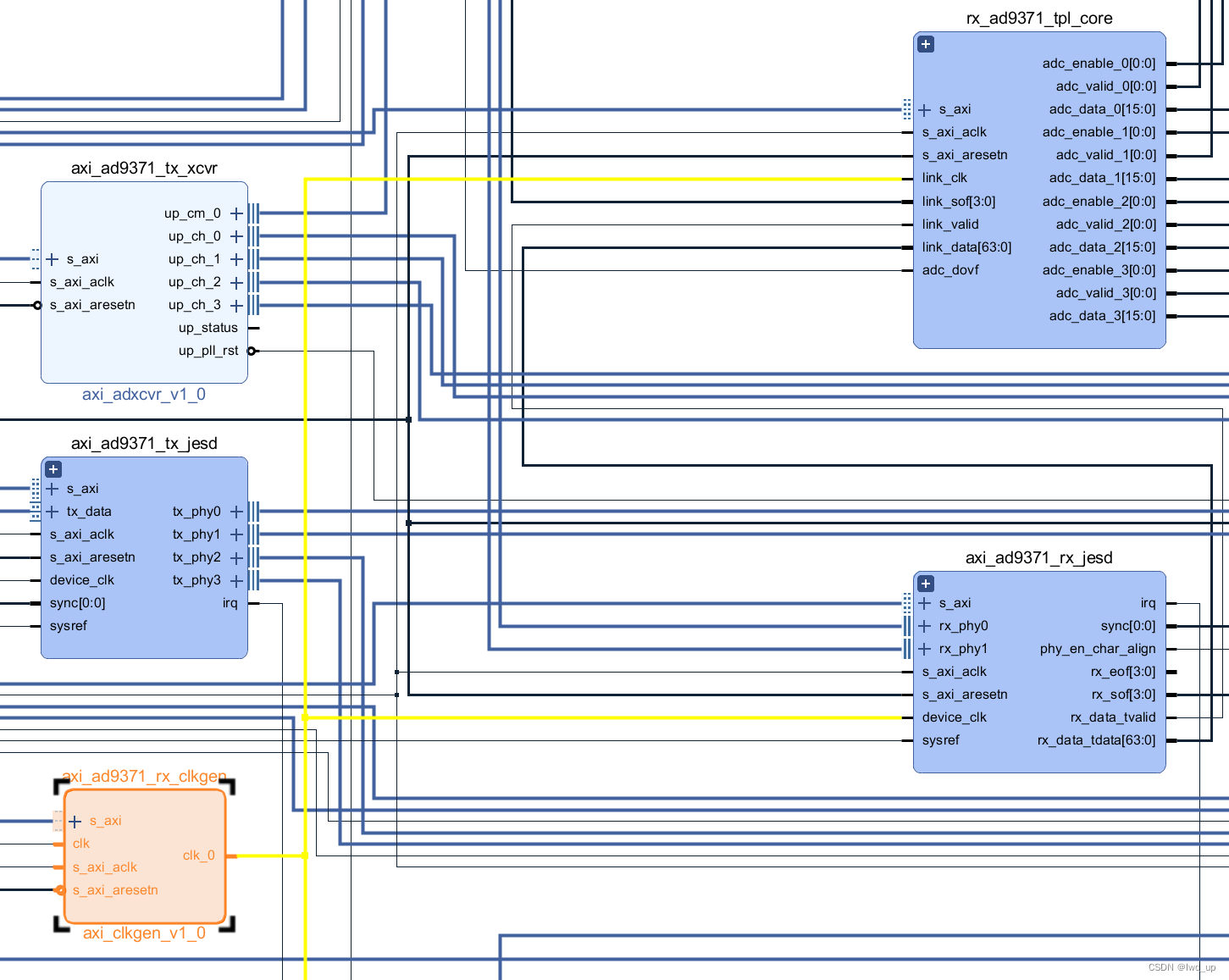

例程中 RXUSRCLK 和 RXUSRCLK2时钟 由 RXOUTCLK 经过BUFG_GT后生成,RXOUTCLK 选择的 RXPLLREFCLK_DIV1 ,又选择的 CPLL 的参考时钟(QPLL0/1 和CPLL 同一个参考时钟),即ref_clk1

BUFG_GT i_rx_bufg (.CE (1'b1),.CEMASK (1'b0),.CLR (1'b0),.CLRMASK (1'b0),.DIV (3'd0),.I (rx_out_clk_s),.O (rx_out_clk));

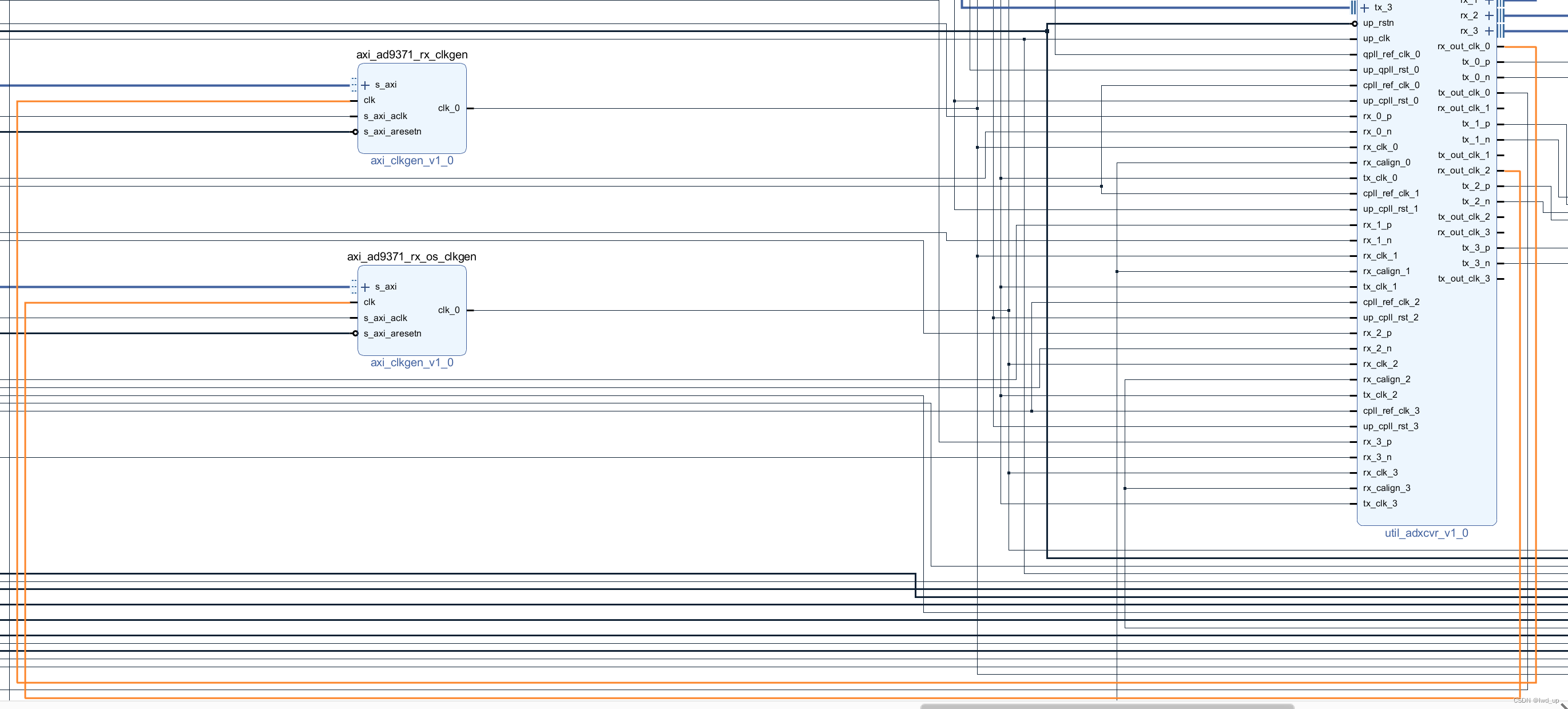

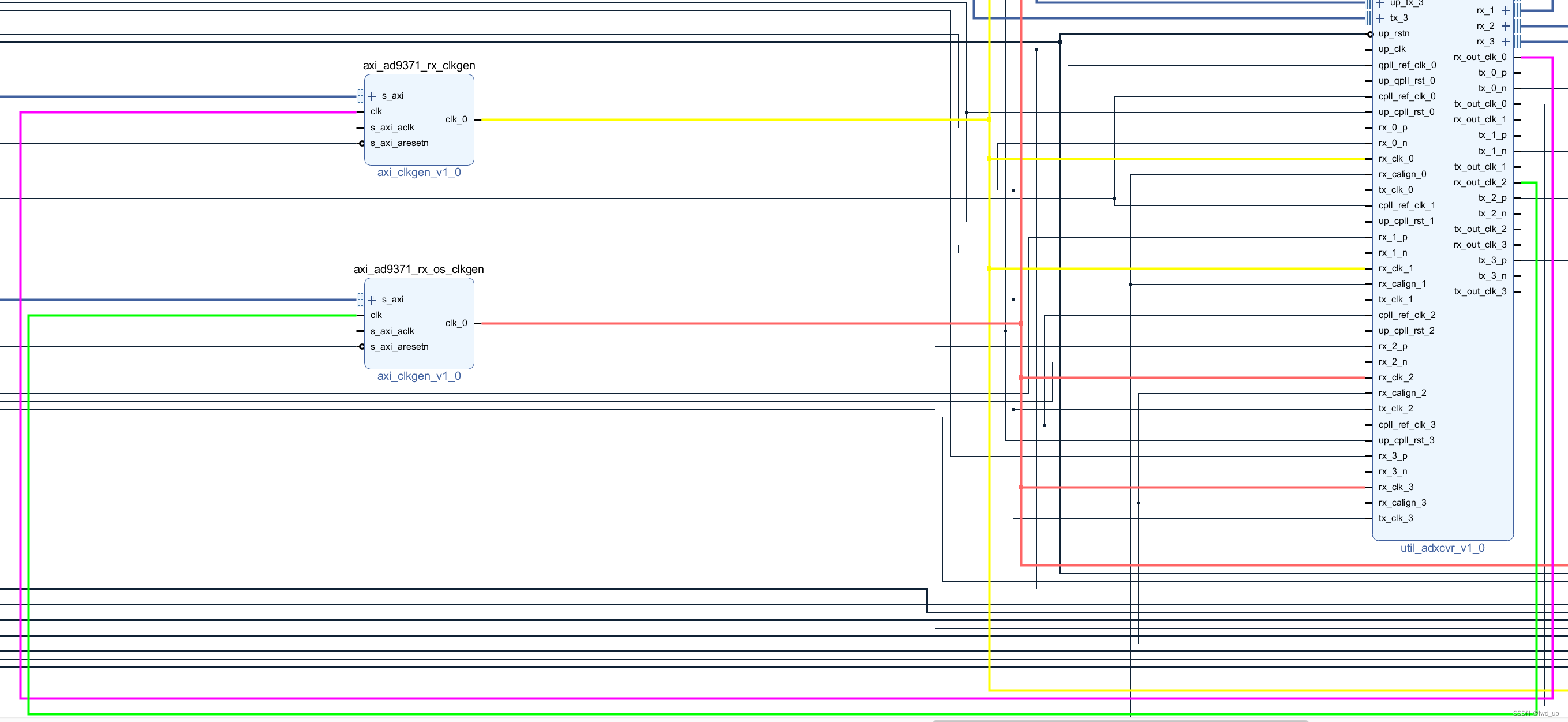

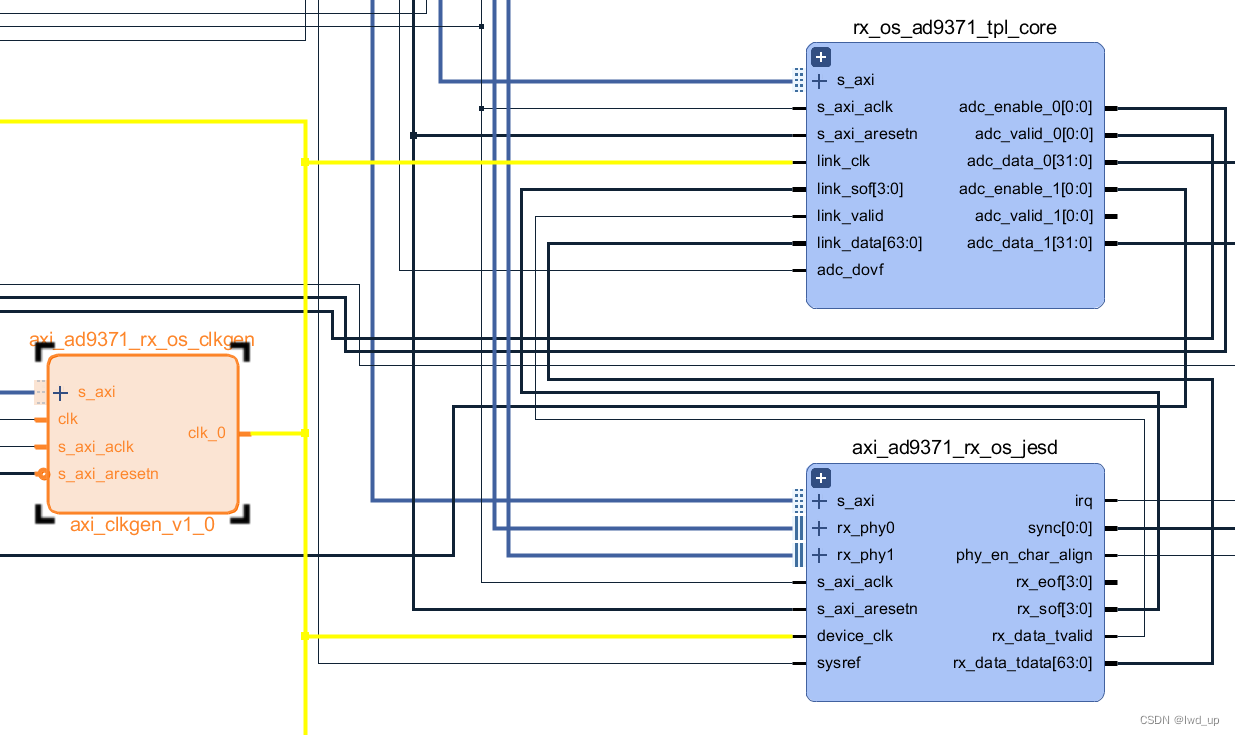

RXOUTCLK 经过BUFG_GT后连接到每个Channel 的 rx_out_clk_< N >,例程使用的rx_out_clk_0和 rx_out_clk_2,输入到axi_ad9371_rx_clkgen和 axi_ad9371_rx_os_clkgen,产生对应的RXUSRCLK、 RXUSRCLK2和Link rate(对于 RX,Channel 0和1的 RXUSRCLK、 RXUSRCLK2和Link rate 速率都是 LineRate/40=4915.2 MHz/40= 122.88;对于 RX_OS,Channel 2和3的 RXUSRCLK、 RXUSRCLK2和Link rate 速率都是 LineRate/40=2457.6 MHz/40= 61.44;)

rx_clk_0、rx_clk_1、rx_clk_2、rx_clk_3 接入每个对应Channel 的 RXUSRCLK 和 RXUSRCLK2

.RXUSRCLK (rx_clk),.RXUSRCLK2 (rx_clk),

生成的 RX link clk 为 链路层 和 传输层 提供 122.88MHz 时钟

rx_jesd status:

Link is enabled

Measured Link Clock: 122.881 MHz

Reported Link Clock: 122.880 MHz

Lane rate: 4915.200 MHz

Lane rate / 40: 122.880 MHz

LMFC rate: 3.840 MHz

Link status: DATA

SYSREF captured: Yes

SYSREF alignment error: No

生成的 RX_OS link clk 为 链路层 和 传输层 提供 61.44MHz 时钟

rx_os_jesd status:

Link is enabled

Measured Link Clock: 61.441 MHz

Reported Link Clock: 61.440 MHz

Lane rate: 2457.600 MHz

Lane rate / 40: 61.440 MHz

LMFC rate: 3.840 MHz

Link status: DATA

SYSREF captured: Yes

SYSREF alignment error: No

rx_adc: Successfully initialized (122880554 Hz)

rx_obs_adc: Successfully initialized (122882080 Hz)

这篇关于AD9371 官方例程HDL详解之JESD204B RX侧时钟生成的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!