本文主要是介绍VHDL:设计16×16bit的寄存器组(代码思路清晰易懂),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

实验内容与要求:

设计16×16bit的寄存器组,要求:

(1)寄存器组中有16个16位的寄存器。

(2)存在复位端,当复位信号有效(如reset=‘0’)时,寄存器组中的16个寄存器清零。

(3)通用寄存器组中有一组数据输入端(如input)、两个地址输入端(如selA,selB)、一个读/写控制端(如WrA)、两组数据输出端(如outputA,outputB)。

VHDL代码如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;entity doublejicunqi is

port(reset: in std_logic; --复位端clk: in std_logic; --时钟s: in std_logic_vector(1 downto 0); --使能端(双端口,所以两位)Address0 , Address1: in std_logic_vector(3 downto 0); --4位的寄存器编号(总共16个寄存器)W_Data: in std_logic_vector(15 downto 0); --待写入数据 Read_data0 , Read_data1 : out std_logic_vector(15 downto 0) --输出数据 );

end doublejicunqi;architecture bedoublejicunqi of doublejicunqi istype my_array is array(15 downto 0) of std_logic_vector(15 downto 0); --16*16位的寄存器组signal reg : my_array;

begin process (reset,clk,s,Address0,Address1) variable i : integer;beginif reset='0' thenfor i in 15 downto 0 loopreg(i) <= "0000000000000000"; end loop;else if clk'event and clk='0' then --下降沿有效if s="10" then reg(CONV_INTEGER(Address0)) <= W_Data;elsif s="11" then reg(CONV_INTEGER(Address1)) <= W_Data; end if; end if; end if; end process;Read_data0 <= reg(CONV_INTEGER(Address0));Read_data1 <= reg(CONV_INTEGER(Address1));

end bedoublejicunqi;测试与分析:

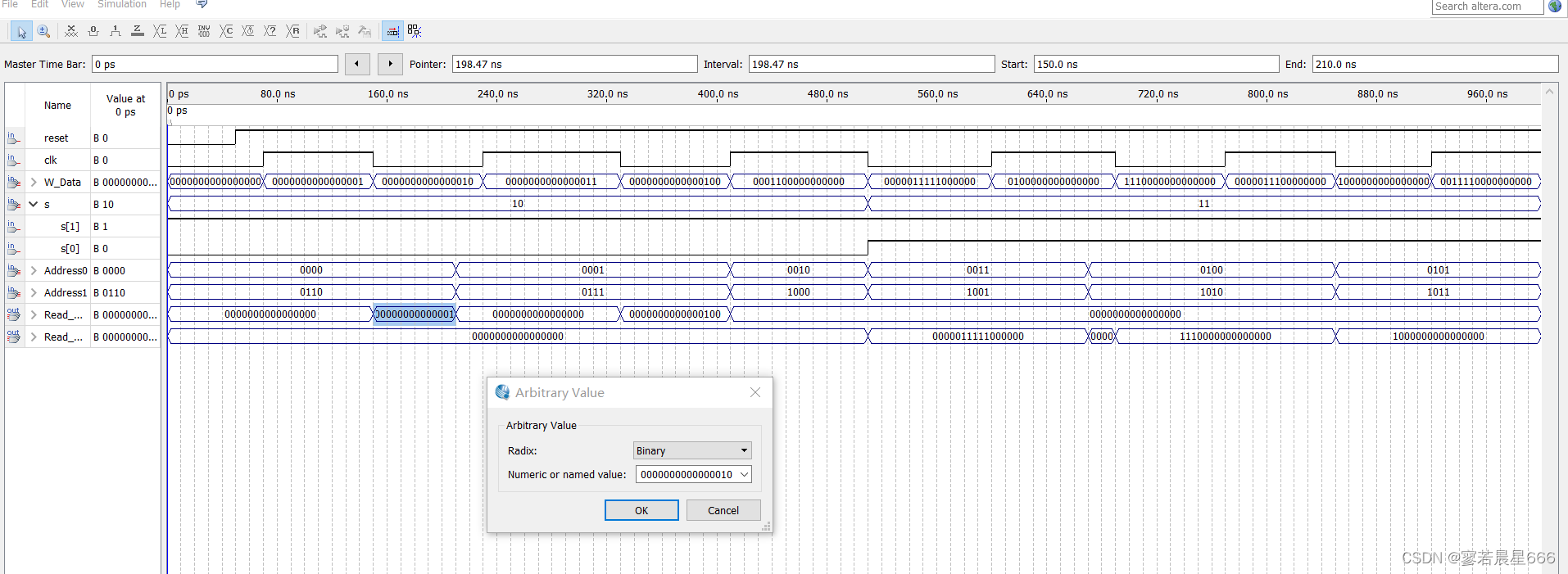

这个设计的是双端口寄存器组。reet是复位端(低电平有效);clk是时钟(下降沿打入数据);W_Data是写入的数据;s是两位的使能端,当它是“10”的时候把数据打入0地址指示的寄存器,当它是“11”的时候把数据打入1地址指示的寄存器; Read_data0 , Read_data1是输出两个数。

在上面这个仿真图中,复位端reset开始一小段为工作状态,把寄存器清零,后面复位端reset不工作,寄存器组处于工作状态。前半段使能端s为“10”,所以把输入的数据打入0地址指示的寄存器,根据我的输入,当时钟clk为下降沿的时候,由于寄存器有延时性,所以把“0000000000000010”打入Read_data1,后面又为下降沿时,把“0000000000000100”依旧打入Read_data1;到后半段使能端s变为“11”,所以把输入的数据打入1地址指示的寄存器,根据我的输入,当时钟clk为下降沿的时候,同样由于寄存器的延时性,把“0000011111000000”打入Read_data2,后面又为下降沿时,“1110000000000000”打入Read_data2,最后同理把“1000000000000000”打入Read_data2。

我写的这个寄存器组的vhdl代码是可以编译通过的,希望可以帮到大家!

求求大家多多支持啦!

这篇关于VHDL:设计16×16bit的寄存器组(代码思路清晰易懂)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!