本文主要是介绍TC3xx A\B SWAP机制的小细节(2),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

1.引入

2.TC3xx Swap机制小细节

3.小结

1.引入

上文TC3xx A\B SWAP机制的小细节(1)-CSDN博客主要把OTA的概念,以及MCU的硬件A\B Swap机制做了简单介绍,下面我们来聊聊TC3xx的SWAP机制

2.TC3xx Swap机制小细节

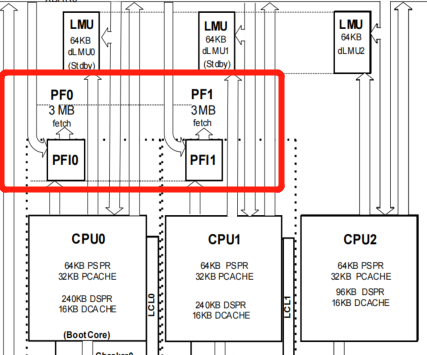

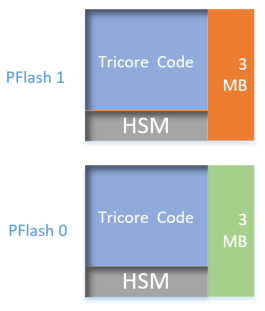

英飞凌TC3xx提供了硬件SOTA机制,它可以实现代码在一个Flash Bank读取并运行,同时另外一个Bank可以刷写新的代码。以TC37x为例,该系列包含两个PFlash Bank,大小均为3MB,如下图所示:

那么我们来思考如下几个问题:

- 要使用swap机制,工程编译应该使用什么地址映射方式?

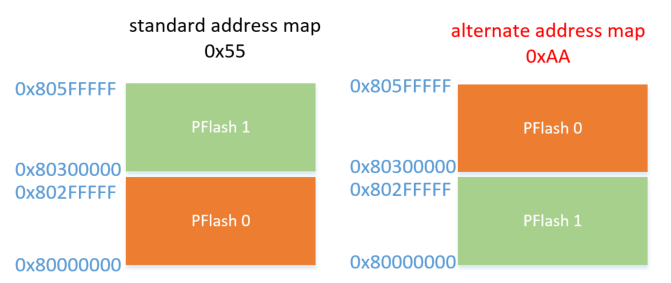

在TC37x系列里,有两个地址映射模式: standard address map和alternate address map,其物理bank和逻辑地址映射关系如下:

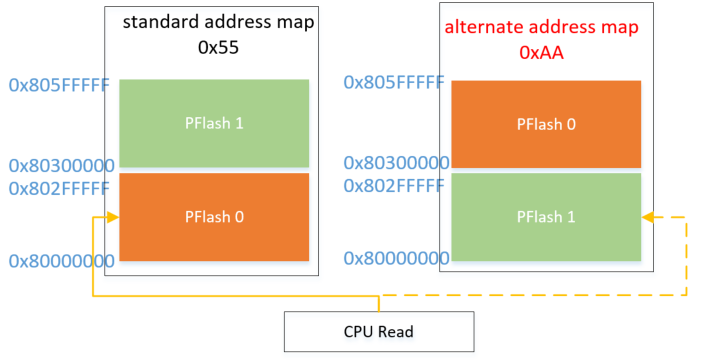

而我们在上面提到使用硬件SWAP机制的好处就是只用维护一个工程以及对应链接脚本,因此从逻辑上讲,我们应该就使用standard address map的地址来设计链接文件并编译工程,整体逻辑如下:

从CPU的视角来看,它始终使用逻辑地址0x80000000(举例)来取指,而芯片硬件根据不同地址映射模式来给物理Bank0、1分配逻辑地址,例如0xAA模式下,分配0x80000000给到PFlash1,这样就能保证运行的是更新后的代码。

- 更新代码应该往哪个地址写数据?

既然CPU始终是从0x80000000(举例)来取指,那么我们就认为这个地址的Bank为Active的Bank,那么很明显我们要将新的代码放进inactive bank里,在该示例中毫无疑问就应该是0x80300000的逻辑地址。

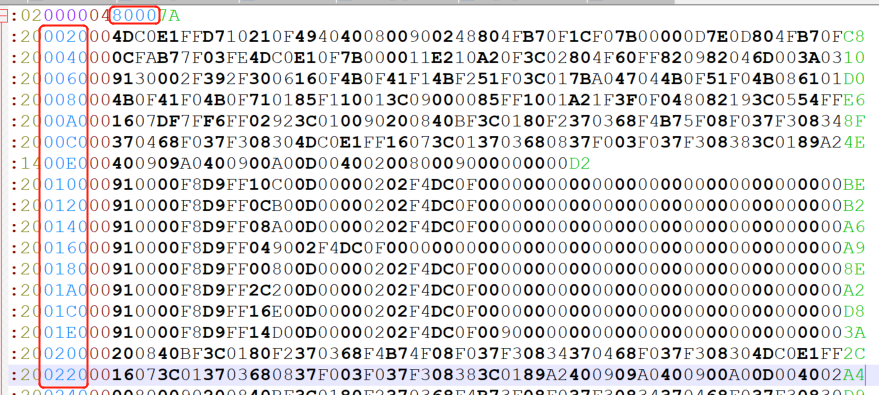

这就出现了问题,一般来说我们通过编译器例如Tasking、Hightec编译出来的文件多数为hex、elf文件,这些文件都是带地址信息的,如下图:

可以看到,第二行记录的起始地址为0x80000020,以此类推。那么我们如果直接用这个hex就覆盖掉了active bank上的内容,这样显然是不行的。

为解决这个问题,Lauterbach、iSystem等等提出了基于调试器级别的方案:

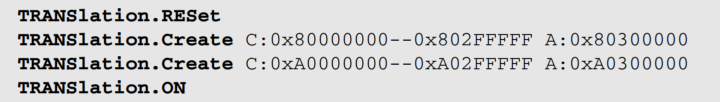

Lauterbach Application Note FLASH Programming TriCore中提到,如果SWAP使能后,Code想要刷进inactive bank,需要使用TRANSlation命令,如下所示:

当然也可以用调试器自带脚本 /demo/tricore/flash/tc3xx-swap.cmmiSystem针对TC3xx的SWAP机制做了优化,用户只需要配置SWAP相应UCB即可完成下载,这个地址偏移等动作对于用户来说是透明的。

Aurix devices have internally more than one program flashes (e.g. PF0, PF1, PF2 flash blocks, etc.). When SOTA is enabled, alternate address mapping is enabled. During download, winIDEA detects which flash memory mapping is selected and it writes data from the download file to correct PFlash block. Download operation is thus transparent to the end user.

那么实际上从整车角度来看,OTA时不能拆盖连接调试器,所以我们只能在Master端进行地址转换,或者我们将待更新文件做成bin文件(不带地址信息),由Master指定刷写的地址。

- 使能HSM时,代码应该如何部署?

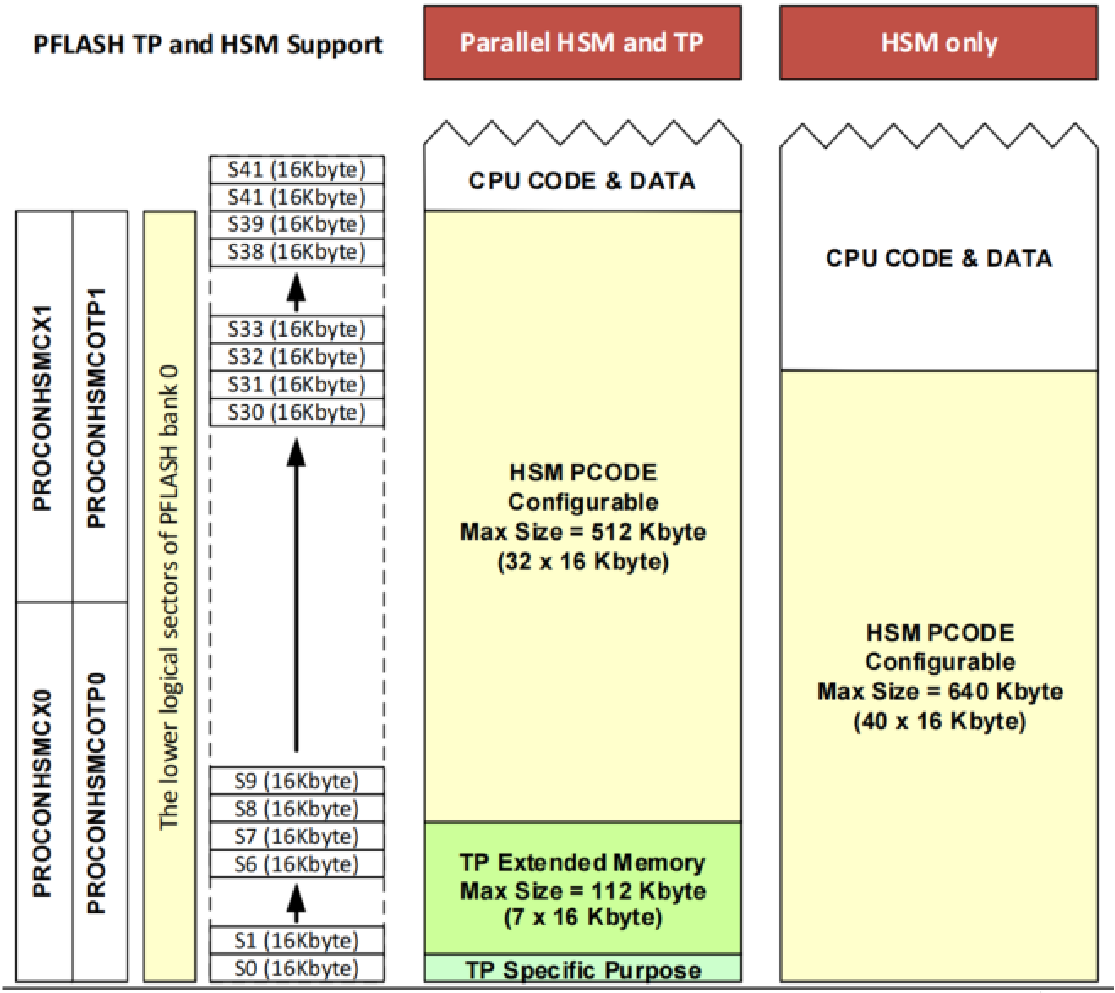

当HSM使能后,TC3xx会给PFlash 0 前40个Sector给到HSM让用户选择,如下图:

既然我们要用A\B SWAP机制,那么inactive bank应该也有相应的镜像,HSM、Host代码部署如下:

同时从手册上描述看,PROCONHSMCX、PROCONHSMCOTP的寄存器设置同样会镜像给到A、B Bank。

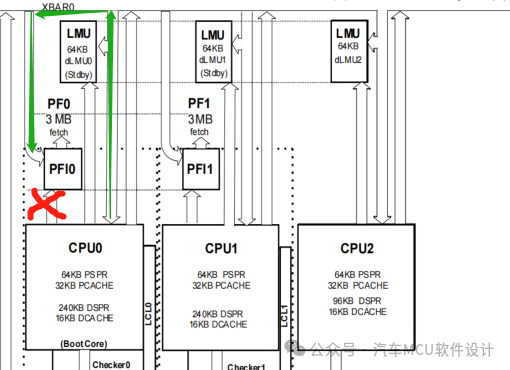

除此之外,我们注意到Tricore CPU都有一个直连接口PFI连接到bank,这里用的是逻辑地址,用于加快取指;而当SWAP使能后,逻辑地址没变,物理Bank却变了,所以CPU只能从SRI去取指,这会有一些性能上的损失,如下:

3.小结

上面简单描述了汽车OTA的必要性,引申出了MCU对于OTA的硬件机制实现,分析了关于TC3xx SWAP小细节,后续我们再继续讲解在OTA硬件机制下为什么Flash的RWW属性非常重要,NXP、ST的Flash RWW有哪些区域。

这篇关于TC3xx A\B SWAP机制的小细节(2)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!