本文主要是介绍FPGA的基础仿真项目--七段数码管设计显示学号,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、设计实验目的

1. 了解数码管显示模块的工作原理。

2. 熟悉VHDL 硬件描述语言及自顶向下的设计思想。

3. 掌握利用FPGA设计6位数码管扫描显示驱动电路的方法。

二、实验设备

1. PC机

2.Cyclone IV FPGA开发板

三、扫描原理

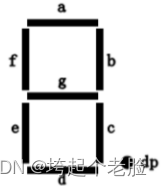

下图所示为1位数码管,由a、b、c、d、e、f、g、dp共8个LED构成,通过点亮特定的LED即可显示相应的字符。

多位的数码管由多个1位数码管构成,如下图所示为4位数码管。为了简化接口电路,多位数码管的段码(a,b,c,d,e,f,g,dp)通常并联在一起,并增加另外的位选信号(如下图中DIG4,DIG3,DIG2,DIG1)来选择使能某一位数码管。位选信号以一定的频率循环使能每一位数码管,从而实现多位字符的显示。

四、设计任务

1. 编写VHDL程序,在开发板的数码管上显示自己学号的末6位数字。

2. (可选)在实现用数码管显示数字的基础上,结合实验一与实验二的内容修改程序,实现一个上升沿触发、异步清零的计数器。具体要求:

(1)在数码管上显示当前的计数值。

(2)触发计数器的时钟频率为1Hz(即计数值每1秒加1),该时钟通过分频得到。

(3)异步清零通过按钮实现。

五、设计要求

1.在Quartus中用VHDL语言编写程序,设计合适的分频器电路和6位数码管扫描驱动电路,仿真验证后,下载至开发板验证设计功能。

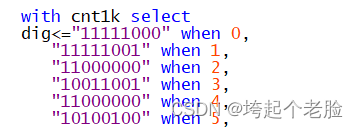

2.开发板上有6位共阳极数码管,即段码(a,b,c,d,e,f,g,dp)输入为0时对应的LED亮,输入为1时对应的LED灭。位选信号(上图中DIG,开发板原理图中SEL)为低有效。自行查看核心板及扩展板原理图来选择正确的引脚进行绑定。

六、解构

示例代码分享

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;entity ledtest is

port(clk : in std_logic;dig : out std_logic_vector(7 downto 0);ds : out std_logic_vector(5 downto 0));

end ledtest;architecture a of ledtest issignal cnt1 : integer range 0 to 31;signal cnt2 : std_logic_vector(9 downto 0);signal cnt1k : integer range 0 to 7;signal clk1m,clk1k : std_logic;begin--clk div by 50process(clk)beginif clk'event and clk='1' thenif cnt1<25 thencnt1 <= cnt1+1;elsecnt1 <= 0;clk1m <= not clk1m;end if;end if;end process;--clk div by 1024process(clk1m)beginif clk1m'event and clk1m='1' thencnt2 <= cnt2 + 1;end if;end process;clk1k <= cnt2(9);--ds scanprocess(clk1k)beginif clk1k'event and clk1k='1' thenif cnt1k<5 thencnt1k <= cnt1k + 1;elsecnt1k <= 0;end if;end if;end process;with cnt1k selectds<="111110" when 0,"111101" when 1,"111011" when 2,"110111" when 3,"101111" when 4,"011111" when 5,"111111" when others;with cnt1k select dig<="10000010" when 0,"10010010" when 1,"10011001" when 2,"10110000" when 3,"10100100" when 4,"11111001" when 5,"11000000" when others;-- "dp g f e d c b a" -- '0' -- "11000000"-- '1' -- "11111001"-- '2' -- "10100100"-- '3' -- "10011001"-- '4' -- "10011001"-- '5' -- "10010010"-- '6' -- "10000010"-- '7' -- "11111000"-- '8' -- "10000000"-- '9' -- "10010000" end a;按照笔者前文进行相应联合Modelsim仿真编译后,进行引脚分配

怎样仿真编译???

给你一个链接自己看:

基于Quartus Prime18.1的安装与FPGA的基础仿真(联合Modelsim)教程-CSDN博客

6.1 引脚分配

注意:原先的引脚项是白色无设置的,如:

需要进行相应引脚的接入,本次实验共阳极,所以引脚如下:(在对应clk一行后Location双击选择对应的Pin引脚)

需要进行相应引脚的接入,本次实验共阳极,所以引脚如下:(在对应clk一行后Location双击选择对应的Pin引脚)

上方是对应的引脚图,编辑后变色

6.2 下载

(看好上方路径,双击打开quartus-->drivers)下载编译驱动程序DPInst.exe

点击下一步,会出现部分无法安装,不用担心,可以正常往下做,点击完成

七、测试结果

(更改数字即从下方代码逆序更改顺序显示)

任务完成

这篇关于FPGA的基础仿真项目--七段数码管设计显示学号的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!