本文主要是介绍ISE14.7工程移植到VIVADO,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Vivado是Xilinx继ISE之后的FPGA开发环境,但是两者的工程存在较大差异,并不能直接转换。

这里主要参考Xilnx手册UG911 (v2018.2) June 6, 2018做相关整理及记录。其中原工程中PL部分的源文件自然可以直接导入,主要问题难点在PS部分:

0、工程导入:这个功能只能导入一部分文件

1、导入zynq soc

首先新建一个空白block design,添加zynq soc,如下图执行XPS导入:

有些参数还需要自己手动比对添加:

2、对于原ISE中的IP但在VIVADO中没有的,可以利用源码的方式添加:

原ISE中的库路径如下:主要都是VHDL源码(VHDL其实和Verilog类似,只是格式比较繁琐,主要分为:entity[模块头部说明]/architecture[模块主体])

比如:AXI Slave Burst这个IP我在VIVADO ip catalog并没有找到:也许改了名字,这是我有疑问的地方

关于VHDL文件使用说明,如果不手动在文件属性栏指定编译的lib库的名字,则默认为work:

UG901 (v2019.1) June 12, 2019 Synthesis

手动指定VHDL的编译库,实际操作发现只能一个一个文档修改:

https://www.cnblogs.com/garylee/archive/2012/11/16/2773596.html

在第1步中zynq soc部分虽然已经同步过来但是其它子模块仍然需要自己手动添加:

ISE中的XPS的操作和VIVADO差距比较大:

ISE中的graphical view不同与vivado diagram,它只能用来查看当前连接的情况,并不能对ip模块进行操作,

实际操作需要切到其它页面:

手动查看原IP参数,依次在vivado中添加进来。

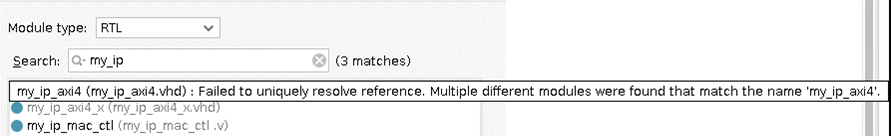

一般来说有源文件的代码都可以在Diagram中右击Add Module,添加进来,但有一些却不可以:

根据UG994中描述:将鼠标悬停在不能添加的文件上面会有相关提示(不过有时候也没有)

导出AXI总线的问题:这个没有找到很好的解决办法,但是应该不影响实际功能:

导出的AXI总线是没有时钟引出的,需要手动导出关联,如果只有一条可以通过如下方法解决:

https://www.cnblogs.com/kingstacker/p/11595978.html

如果有多条则没有很好的办法来消除警告。

关于Diagram中模块内部使用不引出到引脚操作:比如

3、ucf转xdc

主要有两种方案一种利用综合的网表使用write_xdc命令来生成位置约束:

另一种方法借助excel手动将UCF约束转为XDC约束

导入效果如下:

接下来需要一系列操作:

(1)删除空行

(2)刷选字段

如上两步基本可以较方便的把位置约束提取出来了。不得不说Excel确实是好东西!

每一种约束描述,具体可以参看UG911中描述:如KEEPER使用综合保留属性,防止综合时信号优化

最后需要移植的工程太复杂,一般还是用原来的环境:ISE14.7的安装要求如下:

UG631 (v14.7) July 10, 2020

参考连接:

1、https://china.xilinx.com/support/documentation/sw_manuals/xilinx2016_1/ug911-vivado-migration.pdf

2、对于vivado block design操作可以参考文档:UG994 (v2021.1) June 16, 2021Designing IP Subsystems Using IP Integrator

这篇关于ISE14.7工程移植到VIVADO的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!