本文主要是介绍【大学生电子竞赛题目分析】——2023年H题《信号分离装置》,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

今年的大赛已临近落幕,笔者打算陆续对几个熟悉领域的题目作一番分析与讨论,今天首先分析H题。

网上有一些关于H题的分析,许多都是针对盲信号分析的。然而本题具有明确的信号频率范围,明确的信号可能频率,明确的信号波形,明确的信号幅度比,以及明确的信号数量,因此完全不需要采用盲信号分析。况且竞赛参与对象是大学三年级的本科生,要他们进行盲信号分析实在是有些勉为其难了。

其实,除了个别地方的表述不够严谨外,这个题目设计得很有水平。从基本要求到发挥部分,设计难度层层递进,既可以简单完成最基本的部分,也需要深思熟虑才能完成发挥部分。

下面笔者以适合大学本科生的层次,对H题进行分析。抛砖引玉,欢迎大家指正。

一、任务

设计并制作信号分离装置,如图所示。一台双路输出信号源输出2路周期信号A和B(频率范围:20kHz~100kHz,且fA<fB;峰峰值均为1V),经增益为1的加法器产生混合信号C,信号C通过分离电路分离出信号A’和B’。要求信号A’和B’相比信号A和B波形无失真,A’和A、B’和B的波形在示波器上能连续稳定同频显示。

二、要求

1.基本要求

(1)制作增益为1的加法器,实现C=A+B。

(2)信号A和B均为正弦波,fA =50kHz,fB =100kHz。要求装置能正确分离出信号A’和B’,且峰峰值均不小于1V。

(3)信号A和B均为正弦波,频率分别为10kHz的整数倍。要求装置能正确分离出信号A’和B’,且峰峰值均不小于1V。

2.发挥部分

(1)信号A和B分别为正弦波或三角波,频率分别为5kHz的整数倍。要求装置能正确分离出信号A’和B’,且峰峰值均不小于1V。

(2)发挥部分(1)中,信号A和B均为正弦波,且fB是fA的整数倍。要求装置能设置并控制信号B’与A’的初相位差,范围0°~180°,设置分辨率5°,误差绝对值不大于5°。

(3)其他。

三、说明

(1)预留信号A、B、C、A’和B’测试端口。

(2)“加法器”为独立电路板,由移动电源供电,其与“分离电路”只有信号C和地线连接,两者不得存在其他连线或通信方式,否则不予测试。

(3)“分离电路”可配有唯一1个启动键。每项信号分离测试时,设置信号源参数过程中不允许触碰“分离电路”,参数设置完毕后,允许按一次启动键,后续无人工干预。信号分离时间不大于20s。

(4)发挥部分(2)中,令信号A’为sinωA’t,信号B’为sin(ωB’t+φ),本题定义φ为信号B’与A’的初相位差(参见下图)。测试时,设置信号源参数和初相位差后,允许按一次启动键,后续无人工干预。完成时间不大于20s。

(5)“稳定同频显示”的测试方法:设置信号A为示波器触发源,调节水平扫描速度使得示波器上显示4~8个周期的信号A波形,此时观测信号A’波形应与信号A同频率、不失真,稳定显示不漂移。

题目分析与方案设计

本题目要求从一个混合信号中得到两路不同频率的信号,随着题目要求的展开,实现的手段有很大的不同,下面逐一进行分析。

基本要求(1)是一个简单的加法器,说明中要求采用独立电源供电大概是为了避免通过电源传输信息。其实如果不是规定了增益,此加法器完全可以用纯电阻构成无源加法器,不需要电源。

基本要求(2)要求分离两个频率相差1倍(50kHz与100kHz)的正弦信号,这个要求用两个模拟滤波器可以轻松实现。

基本要求(3)也是要求分离两个正弦波,但是两个信号的频率范围是20kHz~100kHz,频率差是10kHz,所以最坏的情况是fA=90kHz、fB=100kHz,这种情况下由于两个信号频率的相对距离很近,用滤波器分离稍有难度,必须采用具有陡峭边沿的椭圆型滤波器。又由于两个频率对于分离电路来说是未知的,所以还需要在分离电路中对输入信号进行FFT分析。得到两个信号频率后,采用程控滤波器构成高阶椭圆滤波器,才可能完成任务。但是由于很多集成程控滤波器(开关电容滤波器)的工作频率上限与Q值都有较大的限制,所以该程控滤波器将是电路设计中的一大难点。

发挥部分(1)规定了两个信号可以是正弦波,也可以是三角波。频率范围为20kHz到100kHz,两个信号的频率间隔是5kHz的整数倍。

这个要求是无法用滤波器实现的。因为三角波的频谱由基频与奇次谐波构成,若fB恰好等于fA的某高次谐波频率,那么这两个信号混合后将无法被滤波器分离。再说,即使不出现上述情况,三角波也无法通过单个滤波器获得(因为要考虑第二个信号,滤波器的带宽受限制),也不可能通过多个滤波器得到其各谐波分量后再组合(因为很难保持各谐波分量之间的相位关系)。

所以要实现发挥部分(1),唯一的手段是信号重建,即先通过对输入信号的频谱分析得到两个信号的基频以及它们的波形,然后设法重建这两个信号。由于题目规定了输入信号的频率范围为20kHz到100kHz之间、5kHz的整数倍,又规定了输入信号只有正弦波与三角波两种波形,所以这个频谱分析还是比较容易做的。具体做法是:先找到两根最高的谱线,它们就是两个输入信号的基频。然后在这两个基频的3倍、5倍等奇次谐波处观察是否存在谱线(高度应是基频的1/9、1/25等),若有则该信号为三角波,若无则为正弦波。

有难度的是信号重建部分。最容易想到的方法是用DDS、PLL频率合成器、或单片机直接产生一个重建信号。但是这个方法的一个致命缺陷是由于原始信号与重建信号之间的基准频率存在不可避免的误差,所以重建信号的频率与原始信号频率不完全相同。题目要求“稳定同频显示”,而按照上述方法重建的信号在显示时会有缓慢的漂移现象。

要做到完全的频率同步就避不开锁相环同步电路。具体地说还有几种不同的解决方案。

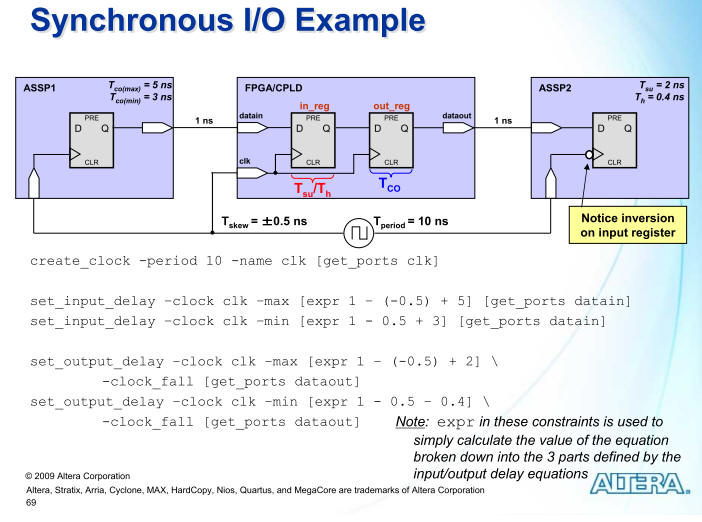

第一个方案是将程控滤波器与锁相环结合,其结构框图如下(图中只画出一路信号,实际电路中有相同的两路)。

此方案中的锁相环可采用经典的PFD鉴相器的集成锁相环电路,例如74HC4046。方案中第一个程控滤波器的作用是获得输入信号中的基频信号,整形后产生矩形波作为锁相环的输入参考频率。由于此信号的波形并无很严格的要求,只要采用陷波器(notch)电路将不需要的那个频率稍作衰减即可,所以此滤波器的设计与制作较为简单。

下图是一个滤波的例子。其中红色波形是两个相同幅度正弦信号的叠加,C=Asin(3ωt)+Bsin(5ωt+φ),蓝色波形是将B信号陷波衰减10dB后的叠加结果,黑色波形是将A信号陷波衰减10dB后的结果。显然,滤波后的信号再经过一个滞回比较器,得到的矩形波的平均频率就是需要的参考频率。尽管此信号的瞬时相位有较大的抖动,但是锁相环具有很好的相位平均作用,所以锁相环的输出频率将严格与原始信号同步。

锁相环的输出为方波信号,经过积分后成为三角波信号,再经过低通滤波器就成为正弦波信号。低通滤波器的截止频率应该根据输出频率改变。由于三角波的幅度受频率影响较大,可以考虑将频率分段,然后根据输出信号频率切换积分电路的积分电阻或积分电容。

第二个方案也是将锁相环与程控滤波器结合,但是省略了上一个方案中稍具困难的第一个滤波器,直接由锁相环完成窄带滤波器的功能。

此方案中锁相环的鉴相器由乘法器构成,压控振荡器附带有振荡频率辅助控制功能。

设输入的混合信号为C=Acos(ωAt)+Bcos(ωBt),压控振荡器的反馈频率为fvco,则乘法器的输出信号中包含 |fvco ± fA| 与 |fvco ± fB| 的基频成分以及 |mfvco ±nfA| 的高次谐波成分。假设VCO的输出频率为fA,则fvco - fA是一个直流分量,其直流电压与两个信号的相位差成比例,而其余分量均为交流分量。鉴相器的输出经过环路滤波器后,所有交流分量被衰减,直流分量用于控制VCO,经过负反馈作用使得锁相环锁定。若VCO的输出频率接近fA但不等于fA,则由于锁相环的频率牵引作用,最后也会达到锁定状态。这种情况下,锁相环等效为一个带宽极窄的窄带滤波器。

工作在这个状态下的锁相环,一定具有很窄的闭环带宽,所以它的捕捉范围是很小的。为了能够锁定在预定的频率,需要将VCO的初始频率设定在预定的锁定频率附近,VCO的整个振荡频率范围也要控制在一个较小的范围内,否则有可能无法锁定,也可能锁定在错误的频率上。但是题目要求的重建信号的频率范围是很宽的,为了解决这个矛盾,方案中设立了振荡频率辅助控制。当通过FFT分析得到输入信号中的两个基频频率后,就通过该辅助控制端口将VCO的中心频率调节到需要锁定的频率,锁相环便可以迅速进入锁定状态,所以是一个辅助锁定电路。

根据采用的VCO的结构不同,该辅助控制可以对VCO注入电压或电流的方式实现。例如对于最常见的HC4046锁相环来说,该芯片中的VCO部分是通过改变引脚12的外接电阻来改变定时电容的充放电偏置电流的,只要如下图在外部用一个压控电流源代替电阻,就可以单片机的DAC输出电压控制VCO的中心振荡频率。

这篇关于【大学生电子竞赛题目分析】——2023年H题《信号分离装置》的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!